# Virtual Fabrication and Analysis of Flexible Micromachined Touch Mode Capacitive Sensor for Pressure Measurement

Abhay Raj Kansal<sup>1</sup>, Amit Gangopadhyay<sup>2</sup>

<sup>1</sup>(Department of Electronics & Communication Engineering, Mangalayatan University, Aligarh, U.P.- INDIA) <sup>2</sup>(Department of Electronics & Communication Engineering, Mangalayatan University, Aligarh, U.P.- INDIA)

**Abstract :** Now a days capacitive touch sensors are widely used in consumer products like MP3 players, mobile phones and other portable devices. More and more the technology is utilized in further application fields such as household appliances as well as automotive and industrial applications. There are several reasons for this development as for reasons of usability, robustness and cost efficiency. Capacitive pressure sensors work by detecting the change in capacitance between a fixed plate and the flexible plate. The major difficulty to the designer is the dimensions and properties used in the simulation of the MEMS devices cannot be exactly followed during fabrication. In order to overcome this problem, we must test the device in simulation for bound of parameters involved in it. This will be done by using Intellisuite software modules like Intellifab, Thermoelectromechanical analysis module, Synple etc.

*Keywords* :*Capacitive Sensing, Dynamic Analysis , Frequency Analysis, Static Analysis, of Capacitive Sensor, Virtual Fabrication.*

# I. INTRODUCTION

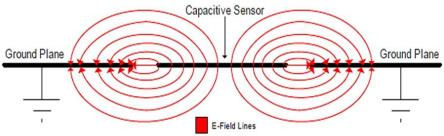

Capacitance describes how the space between two conductors affects an electric field between them. If two metal plates are placed with a gap between them and a voltage is applied to one of the plates, an electric field will exist between the plates. This electric field is the result of the difference between electric charges that are stored on the surfaces of the plates[11]. E-Fields form from the greatest potential to the least potential. Figure 1 shows E-Field lines from the capacitive sensor to ground. On Measuring the capacitance at this point gives the parasitic capacitance.

Fig. 1 E-fields and parasitic capacitance

MEMS based pressure sensors and microphones use an elastic plate as a membrane or a diaphragm as the active mechanical element. As the plate deflects due to the applied pressure, the middle surface remains unstressed. The pressure introduces bi-axial stresses in the plate. Stresses at points is proportional to the distance from the middle surface and the maximum stresses occur at the outer surfaces of the plate. The simplest form of a capacitor consists of two conductors[5], e.g. two metal plates, separated by an insulator. The following formula shows the parameters which influence capacitance:

$$C = \frac{Area \times Dielectric}{Gap}$$

(1)

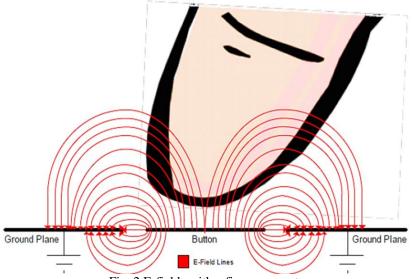

The conductive object allows an increased number of E-Field lines to travel between the sensor and ground. The greater concentration of E-Field lines results in a greater capacitance measured at the sensor as shown in figure 2. In human interface devices, the conductive object is typically a human finger, hand, foot, etc.

Fig. 2 E-fields with a finger present

In ordinary capacitive sensing the size of the sensor, and the dielectric material (air) remain constant. The only variable is the gap size. Based on this assumption, driver electronics assume that all changes in capacitance are a result of a change in gap size. The electronics are calibrated to output specific voltage changes for corresponding changes in capacitance. These voltages are scaled to represent specific changes in gap size. The amount of voltage change for a given amount of gap change is called the sensitivity[5][12]. By using Intellisuite Tools, all the designing or fabricating and different types of analysis or simulation was performed at virtual level here.

The only variable is the gap size. Based on this assumption, driver electronics assume that all changes in capacitance are a result of a change in gap size. The electronics are calibrated to output specific voltage changes for corresponding changes in capacitance. These voltages are scaled to represent specific changes in gap size. The amount of voltage change for a given amount of gap change is called the sensitivity[3][4].By using Intellisuite Tools, all the designing or fabricating and different types of analysis or simulation was performed at virtual level here.

#### II. INTELLIMASK

It is a Mask layout design tool for MEMS devices. IntelliMask is specially use for constructing and editing MEMS device level masks.

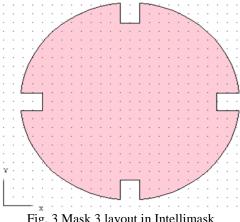

Fig. 3 Mask 3 layout in Intellimask

In this we create three cicular masks of three different radius which are 45  $\mu$ m, 50  $\mu$ m and last mask is of 55  $\mu$ m. The last mask has a different shape where four rectangles are create on the outer surface of circle at equal distances to allow the electric field lines path on the uppre section of the sensor. These masks were used at the time of virtual fabrication of the device.

# III. INTELLIFAB

Intellifab allows us to construct 3D models directly from the process steps and then export them to the analysis modules. Here we analyse the methods for determining material properties from fabrication and operating parameters which are very important from device making point of view. So it is a fabrication based computer aided designing using virtual fabrication techniques.

By this tool we create or fabricate capacitor sensor device using the two methods where we use different materials for both the devices. First capacitor sensor diaphragm is made by polysilicon material and silicon substrate is doped through the P ions whereas second capacitor sensor diaphragm is made by silicon nitride and substrate is doped with the B ions. The process steps which we use in fabrication of our devices are shown in table.

| S.NO. | DEVICE 1                                      | DEVICE 2                                                                         |

|-------|-----------------------------------------------|----------------------------------------------------------------------------------|

| 1     | Definition Si czocharlski 100                 | Definition Si czocharlski 100                                                    |

| 2     | Deposition SiO <sub>2</sub> thermal wet       | Deposition SiO <sub>2</sub> thermal wet                                          |

| 3     | Definition X-Ray lithogarphy                  | Definition UV contact                                                            |

| 4     | Etch SiO <sub>2</sub> RIE                     | Etch SiO <sub>2</sub> wet                                                        |

| 5     | Deposition P implant P-ion                    | Deposition B implant B-ion                                                       |

| 6     | Etch SiO <sub>2</sub> RIE                     | Etch SiO <sub>2</sub> wet                                                        |

| 7     | Deposition PSG LPCVD generic                  | Deposition PSG LPCVD generic                                                     |

| 8     | Definition UV contact                         | Definition UV contact                                                            |

| 9     | Etch PSG wet sacrifice                        | Etch PSG wet sacrifice                                                           |

| 10    | Deposition Polysilicon LPCVD SiH <sub>4</sub> | Deposition Si <sub>3</sub> N <sub>4</sub> LPCVD SiH <sub>2</sub> Cl <sub>2</sub> |

| 11    | Definition X-Ray lithography                  | Definition UV contact                                                            |

| 12    | Etch Polysilicon dry SF <sub>6</sub> plasma   | Etch Si <sub>3</sub> N <sub>4</sub> RIE                                          |

| 13    | Etch PSG wet sacrifice                        | Etch PSG wet sacrifice                                                           |

| 14    | Etch Si wet KOH                               | Etch Si wet sacrifice                                                            |

#### **3.1 Definition of Silicon Substrate**

Silicon is one of very few materials that is economically manufactured in single crystal substrates. This crystalline nature provides significant electrical and mechanical advantages . Here we prefer to use the (100) plane rather than (010) or (111) plane because many alkaline aqueous solutions, such as potassium hydroxide (KOH), selectively etch the (100) planes of silicon but not the (010) or (111) planes which means the [100] is the easiest direction for etching, and the [111] is the hardest direction for etching. [1].

Crystalline silicon is a hard and brittle material deforming elastically until it reaches its yield strength, at which point it breaks. Its tensile yield strength is 7 GPa, which is equivalent to a 700-kg weight suspended from a 1-mm2 area. Its Young's modulus is dependent on crystal orientation, being 130 GPa in [100] directions—near that of steel but is as light as aluminium with a mass density of 2.3g/cm3. It has melting point at 1400°C, which is about twice as high as that of aluminium Silicon is also well known to retain its mechanical integrity at temperatures up to about 700°C [1][2]. Here we use the  $140\mu$ m×140µm square silicon substrate which is of 5000nm or 5µm thick.

# 3.2 Deposition of Silicon diOxide

Silicon dioxide is used as an electric insulator as well as for etching masks for silicon and sacrificial layers. This is also used as sacrificial layers in surface micromachining processes because this can be preferentially etched with high selectivity to silicon. There are several ways silicon dioxide can be produced on substrate surfaces. But the least expensive way to produce  $SiO_2$  film on the silicon substrate is by thermal oxidation.  $SiO_2$  can be produced over the surface of silicon substrates by growing SiO2 with dry O2 in the air or wet steam at high temperature:

$$Si (solid) + O_2 (gas) \rightarrow SiO_2 (solid)$$

(2)

Si (solid) + 2H<sub>2</sub>O (steam)

$$\rightarrow$$

SiO<sub>2</sub> (solid) + 2H<sub>2</sub> (gas) (3)

We use wet process to deposit the  $SiO_2$  layer of 425 nm on both side of silicon substrate. For this we set temperature to 960°C and apply pressure of 101325 Pa.

#### 3.3 Masking and Photography by UV and X-Ray

A mask is transparent plate with the some thickness, parts of which are covered with some non transmitting material in order to create a pattern on the semiconductor wafer when illuminated with light or radiation. Here we use circular mask which created in intellimask tool previously of 45  $\mu$ m radius. Photoresists are sensitive to light with wavelength ranging from 300 nm to 500 nm. The normal UV light has a wavelength between 350 nm and 500 nm. We use wavelength of 436  $\mu$ m and apply shot of energy 52 J for 10 seconds. In

special applications for extremely high resolution, X-Rays are used. The wavelengths of X-Rays are in the range from 4 Å to 50 Å. We use wavelength of 5 Å and use shot of 35 J for 240 ns. In this step we try to remove the unexposed part of material. For this we set leave photoresist at outside by which the unexposed region of SiO2 is remain after etching process.

#### 3.4 Etching of Silicon diOxides to Unexposed Region

In this step we remove or dissolve the unexposed area of silicon dioxide material by etching process. There are two types of etching techniques wet etching involving the use of strong chemical solvents (etchants), and dry etching using gaseous etchants to remove materials at the desired locations on a substrate.

Wet etchants in aqueous solution offer the advantage of low-cost batch fabrication. There are two types of wet etchants isotropic and anisotropic. The common isotropic etchants is HNA solution while anisotropic etchants are KOH, EDP, and TMAH. With anisotropic etching it is easier to control the etched shape of the substrates. That is why these are also known as orientation-dependent etchants (ODEs) because their etch rates depend on the crystallographic direction. Here we apply wet etchants for 10 minutes to remove the unexposed region of silicon dioxide.

There are three types of dry etching techniques as ion etching, plasma etching, and reactive ion etching. Plasma etching involves the generation of chemically reactive neutrals (F, Cl), and ions (SFx+) that are accelerated under the effect of an electric field toward a target substrate. The reactive species (neutrals and ions) are formed by the collision of molecules in a reactant gas (SF<sub>6</sub>, CF<sub>4</sub>, Cl<sub>2</sub>, CCIF<sub>3</sub>, NF<sub>3</sub>) with a cloud of energetic electrons excited by an RF electric field. When the etch process is purely chemical, powered by the spontaneous reaction of neutrals with silicon, it is referred to as plasma etching. But if ion bombardment of the silicon surface plays a significant role in the chemical etch reaction then the process is referred to as reactive ion etching (RIE). In RIE, ion (SFx+) motion toward the substrate is nearly vertical, which gives RIE vertical anisotropy. Here we apply RF power of 850 W and etch step of 0.5 nm/min.

# 3.5 Ions Implantation

Ion implantation is use in doping of a semiconductor such as silicon substrate with external substances as boron atoms for p type and arsenic or phosphorus atoms for n type doping.

Ion implantation involves forcing of free atoms such as boron or phosphorous with charged particles (ions) into a substrate. The ions whether they are boron ions or phosphorous ions, must carry sufficient kinetic energy to be implanted into the silicon substrate. The ions beam are focused onto the substrate, which is protected by the shield or mask which made of silicon dioxide. The highly energized ions enter the substrate and collide with the electron and nuclei of the substrate. The ions will transfer their all energy to the substrate upon collision, and finally come to a stop at a certain depth inside the substrate.

Here we set the ion dose  $100 \times 10^{12}$  /cm3, ion energy of 8.01025 fJ to reach the depth of 1000 nm or 1  $\mu$ m onto the silicon substrate. Benefit of ion implantation is, it does not require high temperature for the process.

# 3.6 Etching of Remaining Silicon diOxide

Now we remove the remaining silicon dioxide which worked as shield for implantation of ion. For this we use reactive ion etching and wet etching for device 1 and device 2 respectively. By using this process we remove the silicon dioxide layer from both sides.

3.7 Deposition of PSG by LPCVD Process

Fig. 5 Substrate with ion implant after removal of SiO<sub>2</sub>

From this step we start surface micromachining process. The surface micromachining creates 3-D microstructures by adding material to the substrate. Added materials may not be same as the substrate material

for flexibility. Here we require sacrificial layer to create cavity. The sacrificial components are usually made of phosphosilicate glass (PSG) or silicon dioxide deposited on substrates by LPCVD techniques. PSG can be etched more rapidly than silicon dioxide.

For this first we deposit a sacrificial layer of phosphosilicate glass (PSG) through low pressure chemical vapor deposition (LPCVD) where we apply 650oC temperature and a low pressure to 30 min. by which we get 2000 nm or 2 µm thick spacer layer. If at the time of silicon dioxide deposition through LPCVD at low temperature we doped it with phosphorous then we get phosphosilicate glass layer. Due to the low temperature compared to thermally grown oxide, this is known as low-temperature oxide (LTO) layer.

# 3.8 Masking for UV Lithography

Here we use second circular mask of 50 µm radius. In this step we try to remove the exposed part of material which is PSG to create a spacer level. For this we set leave photoresist at inside by which the PSG layer which underneath the mask is remain after the etching process in next step. We use wavelength of 436 µm and apply shot of energy 52 J for 10 seconds.

#### **3.9 Etching of PSG to Exposed Region**

In this step we remove the exposed PSG layer portion. For this we use wet etching process and we use HF etchant solution for 10 min because PSG layer etched more rapidly in it.

# 3.10 Deposition of Polysilicon and Si<sub>3</sub>N<sub>4</sub> by LPCVD

In this step we deposit the diaphragm material of capacitor sensor by LPCVD process of 1500 nm or 1.5 µm where polysilicon and silicon nitride is used for device1 and device 2 respectively. Polysilicon is deposited by the pyrolysis of silane (SiH<sub>4</sub>) to silicon and hydrogen in a LPCVD reactor. For this we apply  $630^{\circ}$ C temperature and a low pressure for 10 minutes.

$$SiH_4 \rightarrow Si + 2H_2$$

(4)

Deposition of Silicon Nitrides used commonly in the semiconductor industry for the passivation of electronic devices because it forms an excellent protective barrier against the diffusion of water, potassium, and sodium ions found in biological environments. Its Young's modulus is higher than that of silicon and its intrinsic stress can be controlled by the specifics of the deposition process by which silicon nitride has been used as a structural material mostly. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) is deposited at atmospheric pressure by reacting silane (SiH<sub>4</sub>) and ammonia (NH<sub>3</sub>), or at low pressure by reacting dichlorosilane (SiCl<sub>2</sub>H<sub>2</sub>) and ammonia.

$$3SiH_4 + 4NH_3 \rightarrow Si_3N_4 + 12H_2$$

$$SiH_2Cl_2 + 4NH_3 \rightarrow Si_3N_4 + 6HCL + 6H_2$$

(5)

(6)

$$3SiH_2Cl_2 + 4NH_3 \rightarrow Si_3N_4 + 6HCL + 6H_2$$

The deposition temperature for either method is between 700°C and 900°C. Both reactions generate hydrogen as a byproduct, some of which is incorporated in the deposited film. If LPCVD silicon nitride is deposited at 800°C to 850°C then it becomes silicon-rich (an excess of silicon in the film) due to a greatly increased dichlorosilane flow rate, that is why we apply 810°C temperature with low pressure to deposit silicon nitride through dichlorosilane.

Fig. 6 Remaining PSG spacerlayer on substrate after etching. Fig. 7 Deposition of diaphragm layer material on substrate. 3.11 Masking for X-Ray and UV Exposure

This is an important step for our device structure point of view. Here we use mask of 55 µm which has a special shape at its edges as shown in figure 3. These cuts are required to pass the electric field lines above device. Here we use X-Ray exposure for device 1 polysilicon material and UV exposure for device 2 silicon nitride diaphragm material. For X-Ray we apply wavelength of 4 Å and use shot of 30 J for 200 ns and for UV exposure we apply wavelength of 436  $\mu$ m and shot of energy 52 J for 15 seconds. We want to remove expose portion of diaphragm material in next step by etching for which we set leave photoresist at inside.

# 3.12 Extra Material Etching of Diaphragm

In this step we remove or dissolve the exposed part of polysilicon and silicon nitride. For polysilicon we use dry plasma etching through  $SF_6$  material to 15 minutes and for silicon nitride we use dry reactive ion etching for 20 minutes. After this step device looks like as shown in figure 8. Still the device is not ready because there is sacrificial layer of phosphosilicate glass is present under the diaphragm cavity. So to remove this PSG material we take another step.

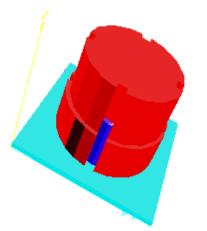

# 3.13 Etching of Sacrificial Phosphosilicate Glass Layer

Here we want to remove the sacrificial layer of phosphosilicate glass which were used as spacer layer to build diaphragm. For this we use wet etching by HF solution for 15 minutes and set etching to sacrificial part.

# 3.14 Removal of Silicon Substrate

Here the last step of sacrificing the silicon wafer was added to isolate the device for ease of simulation purpose in reality the silicon wafer is never sacrificially etched from the device. For both devices we use wet etching where device 1 silicon substrate is etched by HF solution for 20 minutes where as device 2 silicon substrate is etched by KOH solution at 70°C temperature for 5 minutes only. After this step the device looks like as shown in figure 9.

Fig. 8 Device after removal of extra diaphragm material.

Fig. 9 Device after removal of sacrificial and Si substrate.

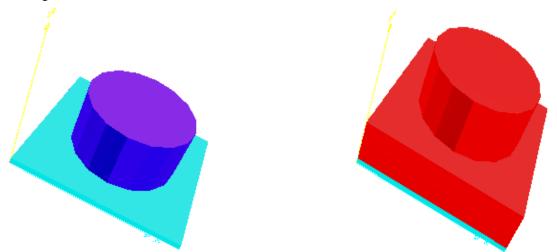

# IV. ELECTROMECHANICAL

It is a fully coupled thermal, electrostatic, mechanical, packing, contact & post-contact analysis and system model extraction tool. Here the device level simulation perform on the device can be categorize into frequency analysis, static analysis, dynamic analysis and system model extraction.

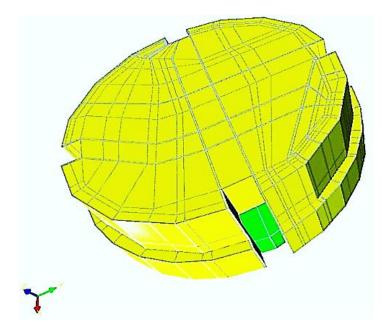

For analysis first we import the fabricated device from intellifab to thermoelectromechanical tool. Here the sensor looks like as shown in figure 10.

Fig. 10 Capacitor sensor in TEM tool

# 4.1 Boundary Conditions

In all mechanical analysis each separate part of the structure (entity) must be assigned at least one fixed boundary to make the problem solvable. Hence we can set the boundary conditions by selecting the appropriate degree of freedom of a particular entity and clicking on the appropriate boundaries.

# 4.2 Natural Frequency Analysis

The natural frequencies of a structure are the frequencies at which the structure naturally tends to vibrate if it is subjected to a disturbance. The deformed shape of the structure at a specific natural frequency of vibration is termed its normal mode of vibration. Hence this simulation computes the natural frequencies and associated mode shapes of a structure including any natural frequency shift due to external forces and/or inplane stresses. Natural frequencies and mode shapes are functions of the structural properties and boundary conditions. If the structural properties change, the natural frequencies change but the mode shapes may not necessarily change. For example if the elastic modulus of the cantilever beam is changed then the natural frequencies change but mode shapes remain the same. If the boundary conditions change then the natural frequencies and mode shapes both change.

| Mode No. | ode No. Natural Frequency (MHz) |          |

|----------|---------------------------------|----------|

|          | Device 1                        | Device 2 |

| Mode 1   | 2.45373                         | 2.86888  |

| Mode 2   | 5.18315                         | 6.05978  |

| Mode 3   | 5.31804                         | 6.21969  |

| Mode 4   | 8.62529                         | 10.08640 |

| Mode 5   | 8.83642                         | 10.32930 |

| Mode 6   | 10.11390                        | 11.82680 |

NATURAL FREQUENCIES OF DEVICE AT RESPECTED MODES

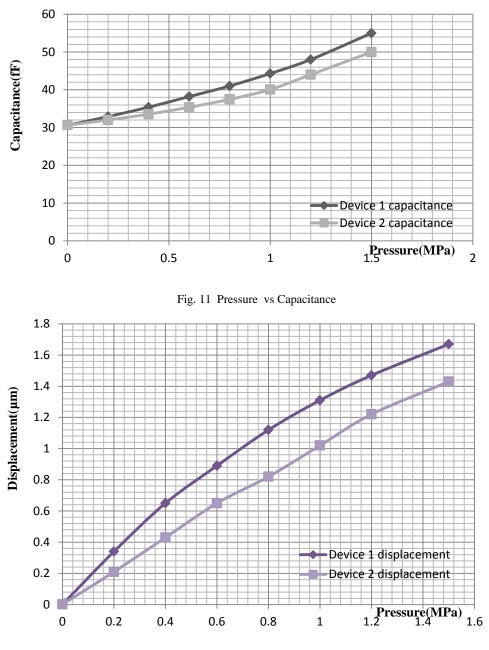

# 4.3 Pressure versus Capacitance Analysis

For pressure versus the capacitance thermoelectro mechanical relaxation is the solution method used in Intellisuite to solve coupled Mechanical Electrostatic analysis. The method implemented uses a boundary element solver to calculate capacitance and charge information and a finite element solver to determine mechanical deformations. Each domain solver is called iteratively, updating the values of its associated variables. This sequence is repeated until convergence is achieved. By this analysis we get capacitance in femto farad between the diaphragm and bottom doped substrate also we get the distance between these two due to applied different pressure values as shown in the figures 11 and figure 12.

Fig. 12 Pressure vs Displacement

As on examine figure 11 and figure 12 we found that capacitance of device 2 in less in comparison of the device 1 which has polysicion diaphragm also the deflection in silicon nitride diaphragm of device 2 is less because stress and stiffness of silicon nitride diaphragm is larger than polysilicon diaphragm.

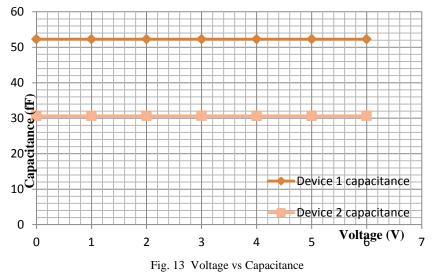

# 4.4 Voltage versus Capacitance

In this analysis we check the behavior of capacitane as we increase voltage at lower levels on regular intervals. After getting the results as shown in figure 13 we found that there is no change in the capacitance of device when we increase the voltage to device.

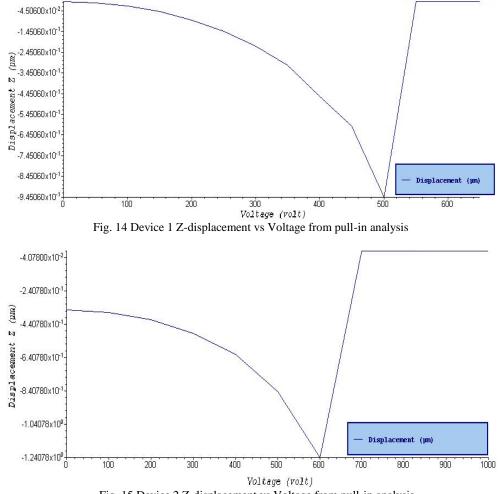

# 4.5 Pull-in Analysis

In this analysis we apply the high Voltage to the device and check the behavioral displacement of diaphragm to substrate. When we apply the voltage of about 0 V and increase it step by step of 100 V to 1000 V then the diaphragm starts falling into downward direction and after reaching its maximum limit of stressing the diaphragm going to damage itself when we increase the voltage level after this threshold point. As shown in the figure 14 and figure 15 the threshold voltage point of polysilicon diaphragm is less in comparison to the silicon nitride diaphragm.

Fig. 15 Device 2 Z-displacement vs Voltage from pull-in analysis

# V. CONCLUSION

This capacitor shall be easy to construct as well as sensitive to human touch in order to enable this as an alternative to mechanical buttons and switches.

The various issues in fabrication, designing and system modeling of integrated pressure sensor devices were analysed by which we found that the device which made by silicon nitride diaphragm has more stiffness and able to tolerate the higher voltage shock upto 600 V rather than 500 V in comparison to the polysilicon diaphragm device and also silicon nitride devices use in biological environments successfully because it has an excellent protectivebarrier against mobile ion diffusion, in particular water, potassium, andsodium ionsfound in biological environments.

But the polysilicon diaphragm device is more sensitive to pressure because this gives more capacitance in comparison to the silicon nitrite diaphragm device. This capacitance is easy to calibrate by using driver electronics. Where all changes in corresponding capacitance will calibrate to output specific voltage changes. These voltages are scaled to represent specific changes in gap size due to pressure.

#### Acknowledgements

I would like to express my most sincere gratitude to Director of Institute of Engineering and Technology, Mangalayatan University for his constant encouragement throughout my research work and also for providing effective management and necessary facilities for laboratory etc. I also like to thanks all the faculty members and the librarians for their kind cooperation and encouragement during the course of work.

#### REFERENCES

- [1]. Maluf, Kirt Williams, *An introduction to microelectromechanicl engineering*, 2nd ed., British Library Cataloguing in Publication Data, 2004, pp. 14–55.

- [2]. Tai Ran Hsu, MEMS & Microsystem Design and Manufactruring, Ed. New Delhi: TATA McGrawhill, 2011, ch. 7, 8, 9.

- [3]. Yafan Zhang, SonbolMassoud-Ansari, GuangqingMeng, Woojin Kim, and Nader Najafi, "An ultra sensitive, high-vaccum absolute capacitive pressure sensor", *IEEE 0-7803-5998-4/01, Integrated Sensing Systems (ISSYS), Inc. Ypsilanti*, MI 48198, 2001.

- [4]. Yang Wei, Russel Torah, Kai Yang, Steve Beeby and John Tudor, "A novel fabrication process for capacitive cantilever structures for smart fabric applications", in *School of Electronics and Computer Science, University of Southampton*, SO17 1BJ, UK 25-27 April 2012.

- [5]. Garron Fish, Mike Dempsey, Juan Gabriel Delgado, Neil Roberts, "Natural frequency analysis of modelica powertrain models", *in* 9th International Modelica Conference, Munich, Germany 10.3384/ecp12076697, September 3-5, 2012.

- [6]. Jon Peterson, "Capacitive sensing 101 PSoC 3 and 5 first touch starter kit" Applications Engineer, *Cypress Semiconductor* Corp. 43674. Oct 2006.

- [7]. Todd O'Connor, "mTouch projected capacitive touch screen sensing theory of operation", *Microchip Technology Inc.* TB3064, DS93064A 2010.

- [8]. Y.Zhang, R. Howver, B. Gogoi and N. Yazdi "A high sensitive ultra thin MEMS capacitive pressure sensor systems", Inc.,M3P.025 Ann Arbor, Michigan, Arizona, USA, Jan 1999

- [9]. Fujitsu Microelectronics, "Capacitive touch sensors application fields, technology overview and implementation example", Germany, *Application: Human Interfaces*, V4, (2010-12)

- [10]. Zack Albus "PCB-based capacitive touch sensing with MSP430" Application Report, SLAA363A June 2007 Revised October 2007

- [11]. Lion Precision (2013) Capacitive sensor theory on how they work, how to use them effectively. [online]. Available:http://www.capacitive-sensing.com/capacitive-sensor-theory.html

- [12]. The embedded core it solutions ecit website. (2014) [online]. Available:http://www.ecitsolutions.com