# A Low Power, 8-Bit, 5MS/s Digital to Analog Converter for Successive Approximation ADC

Amandeep Kaur,

Thapar University, Patiala, India,

**Abstract:** In this paper, a simple switched capacitor Digital to Analog Converter (DAC) is presented that exhibits monotonicity and occupies small area. The proposed DAC starts its conversion from the MSB instead of the traditional approach of starting from LSB making it suitable for use in cyclic or successive approximation analog-to-digital converters. The reference voltage is sampled once and appropriate charge is transferred to the output capacitor of the DAC. Some issues relevant to the design and their possible solutions are presented. The DAC is designed for a resolution of 8-bit. Sampling speed is chosen to be 5MS/s and the main emphasis is on low power. This DAC consumes power in the order of microwatt ( $\mu$ W), compare with previous DACs which consumes more power, generally in the order of milliwatts. The output 8-bits along with power dissipation of 493.8  $\mu$ W has been achieved.

Index Terms—DAC, Folded Cascode, SAR ADC, Transmission gates.

# I. Introduction

Most of real world signals are continuous in time and value called analog signals. But, compared to analog signals, digital signals have many advantages. So, there is a flow to transfer signal processing from the analog domain to the digital one like digital signal processing, which not only allows for a higher level of accuracy but also provides savings in power consumption and silicon area. It increases robustness in the circuit, speeds up the design process, brings flexibility and programmability, and increases the number of chances for design reuse. Because of above benefits of working in digital domain, there is a need to convert the analog real world signals to digital discrete-time and discrete-value signals. DSP processors process digital signals, hence analog to digital converters (ADC) are required to convert the analog signals to digital signals. After processing of signals, the output needs to be converted back to its analog form, hence DAC is used. Here DAC is designed for Successive Approximation ADC which may be further used for bio-medical and video applications.

## II. Background

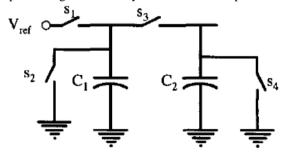

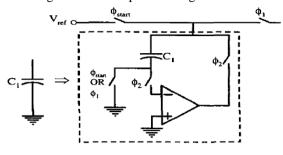

Digital to analog converters operating at moderate speeds and their moderate resolutions are used in many applications. These DACs often consume low power. The classical DAC using two capacitors was proposed in [2] and is shown in Figure 1. The DAC starts its conversion from the LSB. This DAC can be used as a sub-DAC in an ADC, but the ADC will then required to convert the input completely before the LSB becomes available at DAC for processing. This usually slows down the operation of the ADC considerably.

Figure 1: Conventional method of DAC implementation

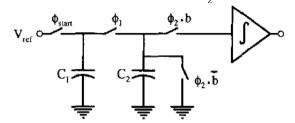

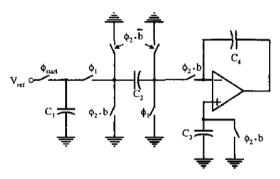

So, a new method of designing DAC is proposed as shown in Figure 2. This low power 5MS/s switched capacitor DAC has been designed in  $0.18\mu m$  CMOS n-well process. The resolution of DAC is taken to be 8-bit. Its practical implementation is shown in Figure 3.

## **III.** Operation Of Dac

$C_1$  and  $C_2$  are chosen to have the same size.  $\varphi_1$  and  $\varphi_2$  are non-overlapping clocks and get enabled only when  $\varphi_{start}$  is low. The conversion process begins with  $\varphi_{start}$  going high. This causes the capacitor  $C_1$  to get charged

to the reference voltage,  $V_{ref}$ . Once  $\varphi_{start}$  goes low,  $\varphi_1$  and  $\varphi_2$  get enabled. Firstly,  $\varphi_1$  turns on which results in charge sharing between  $C_1$  and  $C_2$  and hence  $C_2$  gets charged to  $\frac{V_{ref}}{2}$ .

Figure 2: Proposed DAC structure

The incoming data stream is fed to the DAC with MSB facing first. If the current bit, d, is a 1, the charge which is hold by  $C_2$  is transferred to the integrator. If the bit d is 0, then the capacitor  $C_2$  is discharged to ground. This process continues until the LSB is reached. In each and every cycle, charge is transferred in quantities from the "master" capacitor  $C_1$  to  $C_2$  and hence either integrated with output or discarded to ground in exact correspondence with the bit under conversion. For an N-bit DAC, number of clock cycles required are N to finish the conversion, hence is widely used as an important component in Successive Approximation ADC. At the end of N cycles, the output is available at the output of op amp. All the switches are implemented by using transmission gate.

Figure 3: Practical implementation of DAC

| IV. Dac Design Specifications |  |

|-------------------------------|--|

|-------------------------------|--|

| Table 1: Various design parameters of DAC |                              |  |  |  |  |

|-------------------------------------------|------------------------------|--|--|--|--|

| Parameters                                | Values                       |  |  |  |  |

| Technology                                | Cadence UMC_180nm Technology |  |  |  |  |

| Supply voltage                            | 1.8V                         |  |  |  |  |

| Power                                     | < 500µW                      |  |  |  |  |

| Resolution                                | 8-bits                       |  |  |  |  |

| Sampling speed                            | 5MS/s                        |  |  |  |  |

## V. Op-Amp For Dac

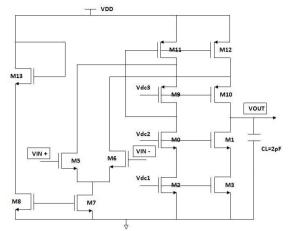

Out of various op amp architectures folded cascode op amp is best suited for switched capacitor applications. So, folded cascode op amp is designed keeping in view the total power consumption of DAC is less than  $500\mu$ W. This power is distributed between op amp and switches, since folded cascode consume more power than the other op amp configurations, hence power budget is divided as  $400 \mu$ W plus  $100 \mu$ W.

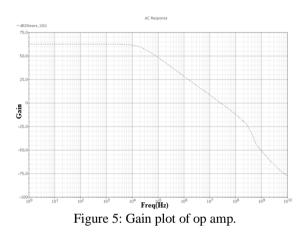

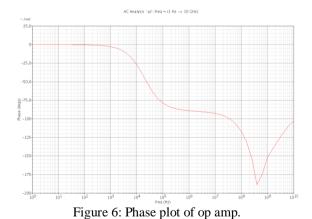

Circuit diagram of folded cascode op amp is shown in Figure 4. With the given power constraint of op amp, the typical corner analysis of op amp gives power consumption of  $306.5 \,\mu$ W. The op amp is made to run at all process corners. Gain and phase plot of op amp is shown in Figure 5 and Figure 6 respectively. The designed op amp meets all the desired specifications. Since resolution of DAC is 8-bit, hence the op amp should have minimum gain of 54.18 dB. Theoretical gain of folded cascode op amp is given by:

$|A_{v}| \approx \{[(g_{m1} + g_{mb3})r_{o3}(r_{o1} \parallel r_{o5})] \parallel [(g_{m7} + g_{mb7})r_{o7}r_{o9}]\}.$

Figure 4: Folded Cascode op amp. Designed op amp provides gain and phase of 62.61 dB and 82.7° respectively.

Given DAC uses transmission gate as a switch. The sampling speed of DAC is given by two factors: the on-resistance of the switch and the value of the sampling capacitor.

Thus, to achieve a high speed, a switch with large aspect ratio and a small capacitor must be used. The value of

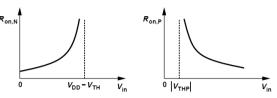

$R_{on}$  i.e. the on-resistance is given by  $R_{on} = \mu_n C_{ox} \frac{W}{L} (V_{DD} - V_{TH})^{-1}$ . Plots of on-resistance of NMOS and PMOS device as a function of input voltage is shown in Figure 7.

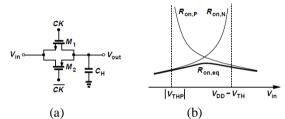

Figure. 7: On-resistance of (a) NMOS and (b) PMOS devices as a function of input voltage In order to accommodate greater voltage swings in a sampling circuit, it is observed that a PMOS switch exhibits an on-resistance that decreases as the input voltage becomes more positive [Figure 7(b)]. It is then possible to employ "complementary" switches so as to allow rail-to-tail swings. Circuit implementation of transmission gate is shown in Figure 8.

#### VII. Switch Designing

The product of the ON-resistance and the capacitive load of the transistor determine the bandwidth. Using, the sampling frequency to be 5Ms/s, the values of R and C can be calculated and hence, the aspect ratio of MOSFET.

Figure 8: (a) Complementary switch, (b) on-resistance of complementary switch.

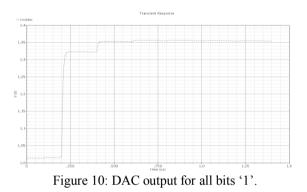

Transmission gates are used as a switch which encounters two main problems: clock feed-through and charge injection. These problems are reduced to minimum by replacing capacitor  $C_1$  in Figure 2 by the circuit shown in Figure 9. Now during  $\varphi_{start}$  the reference voltage  $V_{ref}$  is sampled as before. Again, the circuit looks the same during phase  $\varphi_1$ . However, in phase  $\varphi_2$  at which the voltage on  $C_2$  is being processed, the master capacitor  $C_1$  is placed in the feedback loop of an op amp which forces the voltage across  $C_1$  to remain constant and maintain its level. Any perturbations due to charge injection or charge loss from  $C_1$  are compensated by the op amp. As a result of this, the charge corresponding to the reference voltage sampled across  $C_1$  at the beginning of the conversion process can be hold more accurately. Output of DAC using this proposed method for reducing charge leakage is shown in Figure 10. The DAC is designed for low power consumption. Present work on DAC consumes the power in the order of milli-watts, but this DAC consumes very low power of 493.8  $\mu$ W.

| Table 2: Various performance parameters |         |          |         |         |             |  |

|-----------------------------------------|---------|----------|---------|---------|-------------|--|

|                                         | [6]     | [7]      | [8]     | [9]     | This        |  |

|                                         |         |          |         |         | work        |  |

| Technolog                               | 0.35    | 0.5      | 0.35    | 0.35    | $0.18\mu m$ |  |

| У                                       | $\mu m$ | $\mu m$  | $\mu m$ | $\mu m$ |             |  |

| Resolution                              | 10      | 10       | 10      | 14      | 8           |  |

| Conversion                              | 200     | 400M     | 25MS    | 5MS/    | 5MS/s       |  |

| speed                                   | MS/s    | S/s      | /s      | S       |             |  |

| Input range                             | -       | 0.5      | -       | -       | 0.6-1.3     |  |

|                                         |         | $V_{pp}$ |         |         |             |  |

| Supply                                  | 3V      | 3.3V     | 3V      | 3V      | 1.8V        |  |

| voltage                                 |         |          |         |         |             |  |

| Power                                   | 61m     | 90m      | -       | 7mW     | 493.8       |  |

| consumptio                              | W       | W        |         |         | $\mu W$     |  |

| n                                       |         |          |         |         |             |  |

| Gain                                    | 65d     | -        | -       | 90dB    | 62.61dB     |  |

|                                         | В       |          |         |         |             |  |

| Load                                    | 50pF    | 0.5pF    | 3.2pF   | -       | 2pF         |  |

| capacitance                             |         |          |         |         |             |  |

| VIII. | Performance | Comparison |

|-------|-------------|------------|

|       |             |            |

#### Conclusion IX.

The DAC is designed for resolution of 8-bit.

Sampling speed is taken to be 5MS/s and power dissipation achieved is 493.8 µW. The output of DAC converges to the final value without decreasing from its previous analog value. Simulation results shows that DAC dissipates power of 493.8 µW and output of DAC increases for input'1'. The conversion starts from MSB and the output voltage is obtained using a switched capacitor integrator.

Figure 9: Proposed circuit for reducing charge leakage.

Few of design issues that limit its performance have been discussed. Although no concern on linearity is specifically addressed, various techniques can be used for its improvement also. Such enhancements as well as the design of the improved DAC can be included in the future work. Since the designed DAC failed at SF corner and FS corner because the output of DAC decreases even for "1" input. This problem may be due to charge leakage through capacitor C1 , hence improved charge storage circuit need to be designed to extend this work in future.

#### References

- L. Gallin-Martel, D. Dzahini, F. Rarbi, O. Rossetto "A low power 5 MS/s 14 bit switched capacitors" IEEE,2010 [1]

- R. E. Suarez, P. R. Gray, and D. Hodges, "All-MOS charge redistribution analogue-to-digital conversion techniques-Part 11," IEEE J. [2] Solid-state Circuits, 1975, SCIO,

- pp. 319-385 [3]

- P. Rombouts and L. Weyten, "Linearity improvement for the switched-capacitor DAC," IEEE Electronics Letters, vol. 32, no. 4, [4] pp.293-294, February 1996. U. K. Moon, G. C. Temes, and J. Steensgaard, "Digital Techniques for Improving the Accuracy of Data Converters," IEEE

- [5] Communication Magazine, pp. 136-143, October 1999.

- Mezyad M. Amourah, Saqib Q. Malik and Randall L. Geiger "An MSB-First Monotonic Switched Capacitor Serial DAC" IEEE [6] Circuits and systems, 2002.