# High Speed Voltage Followers- Flipped & Translinear Voltage Follower

Bhautik D. Pandya<sup>1</sup>, Gireeja D. Amin<sup>2</sup>

<sup>1</sup>(E&C Department, L. C. Institute of Technology, India) <sup>2</sup>(E&C Department, L. C. Institute of Technology, India)

**Abstract :** This paper describes two different topology of voltage follower class-A voltage followers and class-AB voltage follower like flipped voltage follower and translinear voltage follower. Each follower has its own advantage and several limitations. The circuits are simulated in CMOS 0.18µm process technology. The two voltage follower characterized using ideal current source and then using a current mirror as a source current. The results are used to compare the performance of the above voltage followers. All analysis was supported by the simulation results. Various topologies of voltage follower like Flipped voltage Follower and Translinear voltage follower are designed in 0.18µm technology with  $\pm 1.8V$  power supply. The analysis are made in terms of gain, bandwidth, offset and transient response using ELDO spice, IC station and Design architect of mentor graphics.

Keywords – Voltage Follower, Buffer, Flipped Voltage Follower, Translinear Voltage Follower.

# I. INTRODUCTION

As the CMOS process entering the nanometer scale analog circuit will need to operate in lower and lower supply voltage. This trend is primarily driven by the need to low power and low voltage requirement on the consumer electronics market. In that, downward revision of voltage technology size do not evolve linearly and  $V_T$ ,  $V_{Dsat}$  not be reduced linearly. These serious facts limit the voltage swing low voltage supply. Many techniques, such as feedback, independent threshold, pseudo differential, Push-pull symmetric, body resulted have been proposed in the literature to reduce the power requirement while maintaining acceptable performance.

# II. VOLTAGE FOLLOWER

A voltage buffer amplifier is used to transfer a voltage from a first circuit, having a high output impedance level, to a second circuit with a low input impedance level. Voltage buffers are essential components in analog and mixed signal processing systems, especially for applications where low signal must be provided to a large capacitive load without being deformed. To fulfill this demand, the input capacitance of the buffer should be as low as possible, so that weak signal is not affected by any circumstance, and the output stage should to have a high rate of rise, so that the performance of the signal can remain driven at high capacitive loads.

Voltage Follower imply that the output will follow the input without any gain. The gain of the circuit is very nearly 1.00. It is useful because its input resistance is very high. It is often used as a buffer between devices to avoid loading errors.

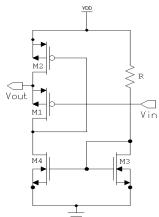

# III. FLIPPED VOLTAGE FOLLOWER

It is essentially a cascade amplifier with negative feedback where the gate terminal of  $M_1$  is used as an input terminal and its source as the output terminal. It is characterized by a very low output impedance due shunt feedback provided by  $M_2$ , high low supply requirement close to a transistor threshold voltage  $V_{TH}$ , low static power dissipation and high gain bandwidth. The flipped (inverted) voltage follower name is based on the fact that FVF is applied on the drain side than on the side of the source. Variation of the output current is absorbed by transistor  $M_2$  which is current sensing transistor, while the current remains constant  $M_1$ , because of this source voltage of the gate of  $M_1$  is constant and remains low distortion even at high frequency. A practical limitation of the FVF cell is that it gives very small input and output signal swing.[4]

Fig.1. Flipped Voltage Follower[3]

The voltage swing is especially important for analog circuits with the trend of supply voltage becoming smaller and the noise almost the same. In order to obtain an acceptable dynamic range the output swing should be sustain as high as possible. The output headroom of flipped voltage follower is decreased to  $V_{gs}$  -2 $V_{Dsat}$  which serious limits the output swing performance in deep sub-micron CMOS process.[1]

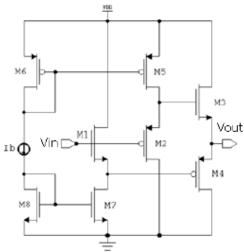

## IV. TRANSLINEAR VOLTAGE FOLLOWER

For the follower to be able to drive low load resistance while at the same time manage large output voltage swing and maintain low harmonic distortion, the other approach is to use a pseudo voltage follower.

Pseudo source follower has a pair of complementary common Drain MOS transistor with two fed back loop consisting of consisting of pair of error of amplifier. Main advantage is its offer low output impedance mainly due to the use of negative feedback.[2]

Fig.2. Translinear Voltage Follower[3]

The circuit consisting of four transistors  $(M_1-M_4)$ . In this transistor  $M_2-M_5-M_6$  create P-type source follower while  $M_1-M_7-M_8$  create N-type source follower. The four transistor  $M_1-M_4$  and  $M_2-M_3$  work as two stage common drain stage and biased by current mirrors implemented by both NMOS $(M_7-M_8)$  and PMOS $(M_5-M_6)$ transistors. Since the M<sub>1</sub> has the same drain current as M<sub>2</sub> and the M<sub>3</sub> has same drain current as M<sub>4</sub>, the gate source voltage of M<sub>1</sub> and M<sub>3</sub> are then nearly equal provided that all NMOS have same dimension and all PMOS have the same dimension. As a result the offset voltage of voltage follower has been minimized. A typical way to reduce the output resistance is to use feedback.

The output resistance and its linearity can also be improved by using local feedback. Since non-linearities possibly result from the current variation in the MOS transistor achieving the follower behavior. Feedback can be used to keep constant the current as shown by the circuit in Figure 4.7. The gain stage amplifies the difference between the input and output of the source follower, thus reducing the output resistance by the amplification of the gain stage itself.

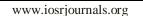

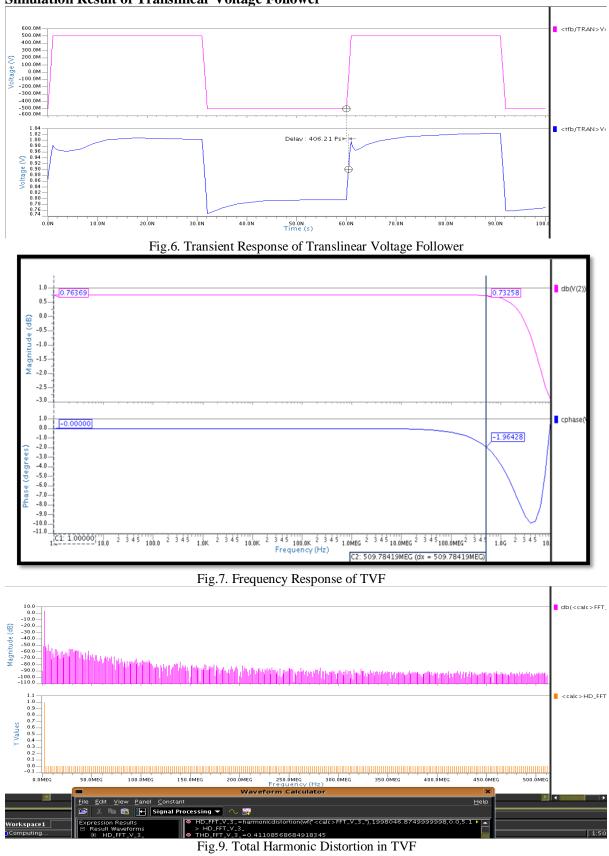

Simulation Result of Translinear Voltage Follower

| TABLE I COMPARISON OF VOLTAGE FOLLOWERS |               |              |                |                                        |

|-----------------------------------------|---------------|--------------|----------------|----------------------------------------|

| Voltage<br>Follower<br>Topology         | Delay<br>(Ps) | Gain<br>(Db) | Band-<br>width | Total<br>Harmonic<br>Distortion<br>(%) |

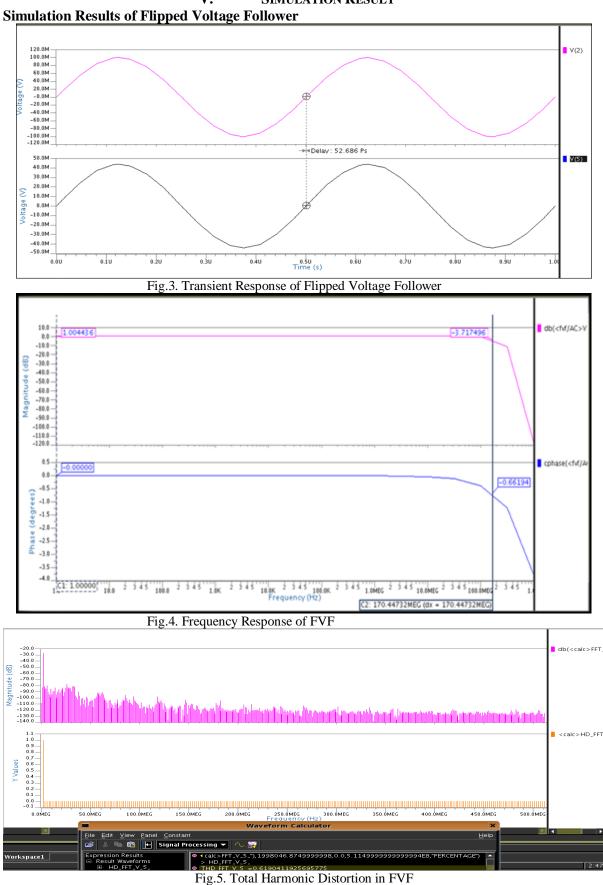

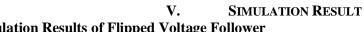

| Flipped<br>Voltage<br>Follower          | 52.686        | 1.0044       | 170.447MHz     | 0.61                                   |

| Translinear<br>Voltage<br>Follower      | 406.21        | 0.763        | 509.784MHz     | 0.41                                   |

VI. RESULTS TABLE I COMPARISON OF VOLTAGE FOLLOWERS

# VII. CONCLUSION

The simulation results for class-A & Class-AB voltage follower is presented in this paper in particular one technology 0.18um. The comparison of these technologies has been summarized in Table I. Where the gain, bandwidth, delay and total harmonic distortion is well compared and shows better performance of circuitry.

### References

## Journal Papers:

- [1] Yaohui Kong, Shuzheng Xu and Huazhong Y, "An Ultra Low Output Resistance and Wide Swing Voltage Follower", ICCCAS 2007, pp. 1007-1010, July 2007.

- [2] Patt Boonyaporn and V. Kasemsuwan, "A High Performance Class AB CMOS Rail to Rail Voltage Follower", IEEE ASIA-Paci\_c Conference on ASIC, pp. 161-163, 2002.

- [3] Gaurang P. Banker, "Comparative Analysis of Low Power CMOS Class-A Voltage Followers with Current Mirror as a Load", IJECT Vol.2, Issue 2, pp. 108-111, 2011.

- [4] Neeraj Yadav, "Low Voltage Analog Circuit Design Based on the Flipped Voltage Follower", IJECSE, vol. 1, no. 2, pp/ 258-273.ISSN.

#### **Books:**

- [5] P. E. Allen and D. R. Holberg, CMOS Analog circuit design, Oxford University Press, 2nd ed., pp. 167-242, 2002.

- [6] Franco Maloberti, Analog Design for CMOS VLSI Systems, Kluwer Academic/Plenum press, 1998.

- [7] Harry W. Li, R. Jacob Baker and David E. Boyce, CMOS Circuit Design, Layout and Simulation, IEEE Press Series on Microelectronics Systems, 2005.

- [8] Stephen H. Lewls, Paul J. Hurst, Paul R. Gray and Robert G. Meyer, Analysis and Design of Analog Integrated Circuits, JOHN WILEY and SONS, 4th ed., 2001.

- [9] Neil H.E. Weste and David Harris, CMOS VLSI DESIGN: A Circuits and System Perspective, Pearson Education, 3rd ed., ISBN 0-321-26977-2, 2005.