# A Novel Implementation of 2x2 Bit Square for Low Power Applications

# B. Dilli Kumar<sup>1</sup>, T. Muni Reddy<sup>2</sup>

<sup>1</sup>Assistant Professor, Department of ECE, Yoganandha Institute of Technology & Science, Tirupati, India <sup>2</sup>Assistant Professor, Department of ECE, Shree Institute of Technical Education, Tirupati, India,

Abstract: Low power has emerged as a principle theme in today electronic industry. Energy efficiency is one of the most important features of modern electronic systems designed for high speed and portable applications. The power consumption of the electronic devices can be reduced by using different design styles. Adiabatic logic style is said to be an attractive solution for such low power electronic applications. This paper presents an energy efficient technique for digital circuits that uses adiabatic logic. The proposed technique has less power dissipation compared to the conventional CMOS design style. This paper evaluates the 2x2 bit square in different adiabatic logic styles and their results were compared with the conventional CMOS design. The simulation results indicate that the proposed technique is advantageous in many of the low power digital applications.

Keywords: Adiabatic, Charge recovery, low power, energy efficient, digital circuits, sinusoidal power clock.

#### I. Introduction

Power consumption plays an important role in the present day VLSI technology. As many of the present day electronic devices are portable, they need more battery backup which can be achieved only with the low power consumption circuits that are internally designed in them. So energy efficiency has become main concern in the portable equipments to get better performance with less power dissipation. As the power dissipation in a device increases then extra circuitry is necessary to cool the device and to protect the device from thermal breakdown which also results in increase of total area of the device. In order to overcome these problems the power dissipation of the circuit is to be reduced by adopting different low power techniques. The less the power dissipation, the more efficient the circuit will be.

From the past few decades CMOS technology plays a dominant role in designing low power consuming devices. Compared to different logic families CMOS has less power dissipation which made it superior over the previous low power techniques. The power consumption in conventional CMOS circuit is due to switching activity of the devices from one state to another state and due to the charging and discharging of load capacitor at the output node.

The power dissipation in conventional CMOS design can be minimized by reducing the supply voltage, node capacitance value and switching activity. But reducing the values of these parameters may degrade the performance of the device. So an efficient low power technique other than CMOS is needed that has less power dissipation compared to CMOS which can be done by using adiabatic technique.

The present paper focuses adiabatic logic which is based on energy recovery principle. In this technique instead of discharging the consumed energy is recycled back to the power supply thereby reducing overall power consumption. In the present paper the performance of 2x2 bit square is evaluated in different adiabatic logic styles and their results were compared with the conventional CMOS design. The performance of this device was evaluated in different adiabatic techniques of ECRL, PFAL, 2PASCL, and PFAL&2PASCL. Simulation results shows that the proposed technique is efficient over the conventional CMOS design in terms of power dissipation.

#### II. Cmos Design

CMOS is the basic building block of many of the digital circuits. The CMOS circuit itself acts as an inverter. It can be realized as a combination of PMOS in the pull up section whose source is connected to power supply and NMOS in the pull down section whose source is connected to ground and the output is taken across the drain junction of the two devices. The CMOS circuit has less power dissipation when compared to many of the previous VLSI families of RTL, TTL and ECL. The power consumption in CMOS is due to the switching activity of the transistors from one state to another state, charging and discharging of the load capacitance and frequency of operation.

#### 2.1 INVERTER

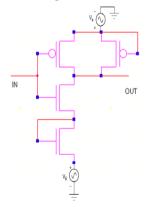

The basic CMOS inverter circuit is shown in figure 1

Fig. 1: CMOS inverter

The operation of the circuit can be evaluated in two stages of charging phase and discharging phase. During the charging phase, the input to the circuit is logic LOW. During this phase, the PMOS transistor conducts and NMOS transistor goes in to OFF state which charges the output value to power supply results in logic HIGH output. The equivalent circuit consists of a resistor in series with the output load capacitance which shows a charging path from power supply to output terminal. Here the resistor acts ac PMOS ON resistor.

Fig. 2: Equivalent circuit for charging process in CMOS

During the discharging phase, the input to the circuit is logic HIGH. During this phase, the NMOS transistor conducts and PMOS transistor goes into OFF state which results in a discharging path from output terminal to ground. The value that is stored at the output during the charging phase discharges towards the ground results in logic LOW output. The equivalent circuit consists of a resistor in series with output terminal to ground. Here the resistor acts as NMOS ON resistor.

Fig. 3: Equivalent circuit for discharging process in CMOS

From the operation of the CMOS design it is evident that during the charging process, the output load capacitor is charged to Q = CLVdd and the energy stored at the output is (½)CLVdd<sup>2</sup>. During the discharging phase, the amount of energy dissipated is also(½)CLVdd<sup>2</sup>. So the total amount of energy dissipated during the charging and discharging phases is

$$E_{\text{dissipated}} = C_L V dd^2$$

(1)

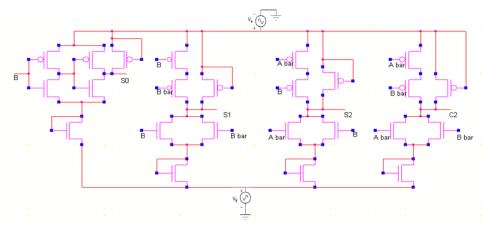

# 2.2 2x2 BIT SQUARE

In many complex multiplications the square of a number can be calculated using multiplier unit. Perhaps it is one of the most time consuming operations in implementing large hardware circuitry. Squaring operation is a special case of multiplication unit. A dedicated square hardware may significantly improve the computation time and reduces the delay to a large extent. The basic circuit for CMOS 2x2 bit square is

Fig. 4: CMOS 2x2 bit Square

The power consumption of the CMOS circuit is based on the following equation

$$P = CV^2f (2$$

From the equation it is evident that the power dissipation of CMOS can be reduced by minimizing the supply voltage, node capacitance and switching activity to some extent. But reducing the values of these parameters may suffer from some disadvantages. Reducing the load capacitance is strongly limited by the technology. Reducing the supply voltage may degrade the performance of the device. Reducing the supply voltage may also suffer from leakage problems.

In order to overcome these problems an efficient low power technique called adiabatic logic is explained in this paper.

#### III. Adiabatic Logic

The word ADIABATIC is derived from the Greek word "adiabatos", which means there is no exchange of energy with the environment and hence no energy loss in the form of heat dissipation. Adiabatic logic is commonly used to reduce the energy loss during the charging and discharging process of circuit operation. Adiabatic logic is also known as "energy recovery" or "charge recovery" logic. As the name itself indicates that instead of dissipating the stored energy during charging process at the output node towards ground it recycles the energy back to the power supply thereby reducing the overall power dissipation and hence the power consumption also decreases. The adiabatic logic uses AC power supply instead of constant DC supply, this is one of the main reasons in the reduction of power dissipation.

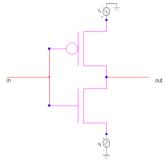

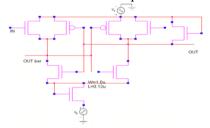

The adiabatic logic can be explained with the help of basic inverter circuit

Fig. 5: Adiabatic inverter

The adiabatic inverter circuit can be constructed using CMOS inverter with two AC power supplies instead of DC supply. The power supply's are arranged in such a way that one of the clock is in phase while the other is out of phase with the first one. The operation of the adiabatic inverter can be explained in two stages. During the charging phase, the PMOS transistor conducts and NMOS transistor goes into OFF state which charges the output load capacitor towards the power supply results in logic HIGH output.

Fig. 6: Equivalent circuit for charging process in adiabatic inverter

During discharging phase, the NMOS transistor conducts and PMOS transistor goes into OFF state. Instead of discharging the stored value at the output towards ground, the energy is recycled back to the power supply. Its equivalent circuit consists of a resistor in series with output load capacitance and power supply.

Fig. 7: Equivalent circuit for charge recovery process in adiabatic inverter

The charging process and the charge recovery process are efficient only when the charging voltage is varying one. Lower the rate of charging, lesser the power drawn from the supply voltage.

# IV. Adiabatic Techniques

Adiabatic logic has a different logic style which helps in the reduction of the power dissipation of the circuit. The present paper explains basic full adder using some of the important adiabatic techniques.

#### **4.1 ECRL**

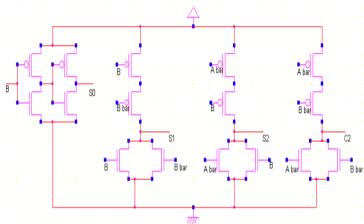

Efficient charge recovery logic consists of two cross couple PMOS transistors in the pull up section where as the pull down section is constructed with a tree of NMOS transistors. Its structure is similar to Cascode Voltage Switch Logic (CVSL) with differential signaling. The logic function in the functional block can be realized with only NMOS transistors in the pull down section. The basic inverter and 2x2 bit square in ECRL logic can be constructed as

Fig. 9: ECRL 2x2 bit Square

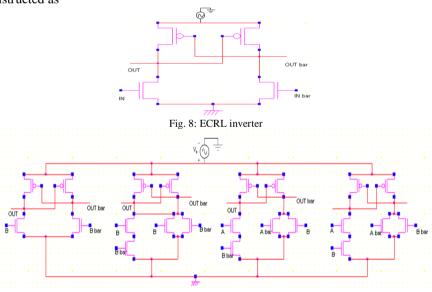

#### **4.2 PFAL**

The Positive Feedback Adiabatic Logic is a partial energy recovery circuit. It is also known as PAL-2N (Pass transistor Adiabatic Logic). The core of PFAL logic is a latch made up of two PMOS and two NMOS transistors that avoid logic level degradation on the output nodes. The logic function in the functional block can be realized with only NMOS transistors connected parallel to the PMOS transistors. The primary advantage of PFAL over ECRL is that the functional blocks are in parallel with the PMOSFETs forming transmission gate. It also has the advantage of implementing both the true function and its complimentary function.

Using PFAL, the basic inverter and 2x2 bit Square can be constructed as

Fig. 11: PFAL 2x2 bit Square

# 4.3 2PASCL

The Two Phase Adiabatic Static Clocked Logic (2PASCL) uses two phase clocking split level sinusoidal power supply's which has symmetrical and unsymmetrical power clocks where one clock is in phase while the other is out of phase. The circuit has two diodes in its construction where one diode is placed between the output node and power clock, and another diode connected between one of the terminals of NMOS and power source. Both the MOSFET diodes are used to recycle charges from the output node and to improve the discharging speed of internal signal nodes. The circuit operation is divided into two phases "hold phase" and "evaluation phase". During the evaluation phase, the power clock swings up and power source swings down. During the hold phase, the power source swings up and power clock swings down.

Using 2PASCL the basic inverter and 2x2 bit Square can be constructed as

Fig. 12: 2PASCL inverter

Fig. 13: 2PASCL Square

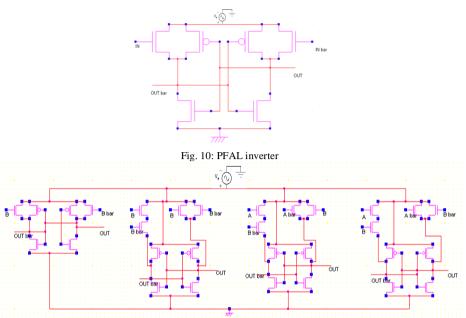

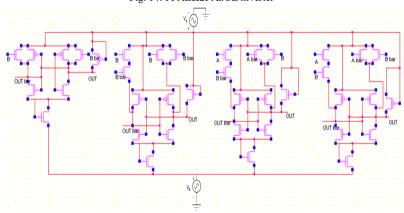

#### 4.4 PFAL& 2PASCL

The PFAL&2PASCL logic can be realized as a combination of both PFAL and 2PASCL. Its structure is similar to 2PASCL except the core part of 2PASCL is replaced by PFAL logic circuit. It has two power clock signals operated in two different modes. The major advantage of this technique is it has less power dissipation compared to ECRL and PFAL and it also gives the true function and complementary function of a given circuit.

Using PFAL&2PASCL, the basic inverter and 2x2 bit Square can be constructed as

Fig. 14: PFAL&2PASCL inverter

Fig. 15: PFAL & 2PASCL Square

# V. Simulation Results And Discussion

The simulation results were verified using PSPICE software at 50 KHz and 50 MHz frequency. The simulation results of 2x2 bit Square in conventional CMOS design and different adiabatic logic design styles were presented in this section

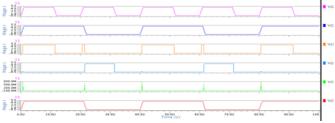

Fig. 16: Simulated waveforms CMOS 2x2 bit Square

Fig. 16 shows the simulated waveforms of 2x2 bit Square, where the top two signals indicate inputs while the bottom four signals are corresponding output signals respectively.

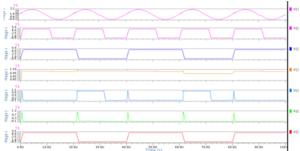

Fig. 17: Simulated waveforms of ECRL 2x2 bit Square

Fig. 17 shows the simulated waveforms of ECRL 2x2 bit Square, where the uppermost signal indicate sinusoidal power clock, the two signals below it are input signals and the bottom four signals are corresponding output signals respectively.

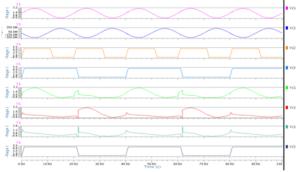

Fig. 18: Simulated waveforms of PFAL 2x2 bit Square

Fig. 18 shows the simulated waveform of PFAL 2x2 bit Square, where the uppermost signal indicates sinusoidal power clock, the two signals below it indicate inputs and the lower four signals are corresponding output signals respectively.

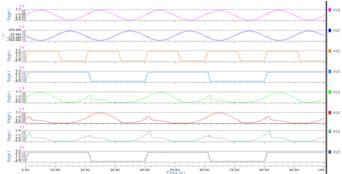

Fig. 19: Simulated waveforms of 2PASCL 2x2 bit Square

Fig. 19 shows the simulated waveform of 2PASCL 2x2 bit Square, where the top two signals indicate sinusoidal power clocks, the signal between power clocks are two inputs and corresponding output signals respectively.

Fig. 20: Simulated waveforms of PFAL&2PASCL 2x2 bit Square

Fig. 20 shows the simulated waveforms of PFAL&2PASCL 2x2 bit Square, where the top two signals indicate sinusoidal power clocks and the signals below the power clocks are two inputs and four output signals respectively.

TABLE 1: Comparison of different parameters of 2x2 bit Square in adiabatic logic with CMOS

| Logic style | Power                          | Memory Space                                                                                  | Average no. of                                                                                                                                                                                                                                                        | Number of                                                                                                                                                                                                                                                                                                                                                              | Latency                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|--------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | dissipation                    | allocated                                                                                     | Newton                                                                                                                                                                                                                                                                | transistors                                                                                                                                                                                                                                                                                                                                                            | (%)                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | (Watts)                        | (bytes)                                                                                       | iterations                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CMOS        | 1.6299 E-10                    | 43294720                                                                                      | 3.730693                                                                                                                                                                                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                     | 0.0000                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ECRL        | 5.8180 E-11                    | 43286528                                                                                      | 3.716253                                                                                                                                                                                                                                                              | 26                                                                                                                                                                                                                                                                                                                                                                     | 0.0000                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PFAL        | 2.4315 E-11                    | 43278336                                                                                      | 3.612121                                                                                                                                                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                     | 0.0000                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2PASCL      | 1.2389 E-11                    | 43286528                                                                                      | 4.054118                                                                                                                                                                                                                                                              | 28                                                                                                                                                                                                                                                                                                                                                                     | 0.0000                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PFAL&2PASL  | 3.9931 E-11                    | 43728896                                                                                      | 4.556150                                                                                                                                                                                                                                                              | 42                                                                                                                                                                                                                                                                                                                                                                     | 0.0000                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | CMOS<br>ECRL<br>PFAL<br>2PASCL | dissipation (Watts)  CMOS 1.6299 E-10  ECRL 5.8180 E-11  PFAL 2.4315 E-11  2PASCL 1.2389 E-11 | dissipation<br>(Watts)         allocated<br>(bytes)           CMOS         1.6299 E-10         43294720           ECRL         5.8180 E-11         43286528           PFAL         2.4315 E-11         43278336           2PASCL         1.2389 E-11         43286528 | dissipation<br>(Watts)         allocated<br>(bytes)         Newton<br>iterations           CMOS         1.6299 E-10         43294720         3.730693           ECRL         5.8180 E-11         43286528         3.716253           PFAL         2.4315 E-11         43278336         3.612121           2PASCL         1.2389 E-11         43286528         4.054118 | dissipation (Watts)         allocated (bytes)         Newton iterations         transistors           CMOS         1.6299 E-10         43294720         3.730693         20           ECRL         5.8180 E-11         43286528         3.716253         26           PFAL         2.4315 E-11         43278336         3.612121         34           2PASCL         1.2389 E-11         43286528         4.054118         28 |

Table 1 show that the power dissipation of different adiabatic logic styles is lesser than the conventional CMOS design. The power supply that is given to the adiabatic circuits is also lesser than the conventional CMOS design.

#### VI. Conclusion

This paper proposes energy efficient adiabatic logic for digital circuits. The results were simulated using PSPICE and comparison has been done for different parameters of 2x2 bit Square in different adiabatic logic styles and CMOS design. The results show that the proposed adiabatic logic has less power dissipation compared to conventional CMOS design and it also uses less power supply. These advantages made this logic more convenient for energy efficient digital applications.

#### References

- [1] B. Dilli Kumar, M. Bharathi, "Design of Energy Efficient Arithmetic Circuits Using Charge Recovery Adiabatic Logic" in International Journal of Engineering Trends and Technology, 2013.

- [2] Atul Kumar Maurya and Ganesh Kumar, "Adiabatic Logic: Energy Efficient Technique for VLSI Applications", International Conference on Computer& Communication Technology (ICCCT)-2011.

- [3] Vojin G. Oklobd"zija, Dragan Maksimovi' c, "Pass-Transistor Adiabatic Logic Using Single Power-Clock Supply ", IEEE Transactions on Circuits and Systems, Vol. 44, No. 10, October 1997.

- [4] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low power CMOS digital design," *IEEE J. Solid-State Circ.*, vol. 27, no. 4, pp.473-484, Apr. 1992.

- [5] T. Indermauer and M. Horowitz, "Evaluation of Charge Recovery Circuits and Adiabatic Switching for Low Power Design," Technical Digest IEEE Sym. Low Power Electronics, San Diego, pp. 102-103, Oct. 2002.

- [6] Arsalan, M. Shams, M., "Charge-recovery power clock generators for adiabatic logic circuits", 18th International Conference on VLSI Design, pp. 171-174, 3-7 January 2005.

- [7] Dragan Maksimovic et al, "Clocked CMOS adiabatic Logic with Integrated Single Phase Power Clock Supply", IEEE Transactions on VLSI Systems, vol 8, No 4, pp 460-463, August 2000.

- [8] W.C. Athas, L. Svensson, J.G. Koller et ,N.Tzartzanis and E.Y.Chou: "Low-power Digital Systems Bared on Adiabatic-switching Principles". IEEE Transactions on VLSI Systems. Vol. 2, No. 4, pp. 398-407 December. 1994.

- [9] Satyam Mandavilli, Prashanth Paramahans "An Efficient Adiabatic Circuit Design Approach for" International Journal of Recent Trends in Engineering, Vol 2, No. 1, November 2009 Low Power Applications.

- [9] A. Vetuli, S. Di Pascoli, and L.M. Reyneri, "Positive feedback inadiabatic logic," Electron.Lett.,vol.32, pp.1867-1869, Sept. 1996.

- [10] N. Anuar, Y. Takahashi, T. Sekine, "Two phase clocked adiabatic static CMOS logic," proc. IEEE SOCC 2009, pp. 83-86, Oct. 2009.

- [11] N. Anuar, Y. Takahashi, T. Sekine, "Two-Phase clocked adiabatic static CMOS logic and its logic family" Journal of semiconductor technology and science, vol 10, no. 1, Mar. 2010.

#### Authors

Mr. B. Dilli kumar , Assistant Professor, Department of ECE, Yoganandha Institute of Technology & Sciences, Tirupati, India. He has completed M.Tech in VLSI from Sree Vidyanikethan Engineering College, Tirupati. His research areas are Low power VLSI, Digital IC Design, VLSI and Signal processing

Mr. T. Muni Reddy, Assistant Professor, Department of ECE, Shree Institute of Technical Education Tirupati, India. He has completed M.Tech in Embedded Systems from SRM University. His research areas are Digital System Design, VLSI Signal Processing, Embedded Systems.