# Low power/ Low Voltage Cross Coupled SRAM – Based on Schmitt Trigger

Lalitha Sowmya.M<sup>1</sup>, S. Jagadeesh<sup>2</sup>, Lakavath.Mohan<sup>3</sup>

Asst. Prof, Department of ECE, SSJ Engineering college, V. N. Pally, JNTUH – Hyderabad, A.P.

Assoc. Prof & HOD of ECE, SSJ Engineering college, V.N. Pally, JNTUH - Hyderabad, A.P, 500075.

M. Tech Student, Department of ECE, SSJ Engineering college, V.N. Pally, JNTUH - Hyderabad, A.P.

**Abstract:** In this paper we are going to modify the Schmitt Trigger based SRAM for the purpose of more reduced power & area than the existing type of designs as well as the new design which is combined of virtual grounding with read Error Reduction Logic is compared with the existing technologies & the nanometer technology is also improved for the purpose of much improved reduction of area & power factors than the Schmitt Trigger based SRAM Designs the simulations were done using microwind & DSCH results **Key words:** CMOS, DSCH, SCHMITT- TRIGGER, SRAM, MICROWIND.

# I. Introduction

As microprocessors and other electronics applications get faster and faster, the need for large quantities of data at very high speeds increases, while providing the data at such high speeds gets more difficult to accomplish[1][2]. As microprocessor speeds increase from 25 MHz to 100 MHz, to 250 MHz and beyond, systems designers have become more creative in their use of cache memory, inter leaving, burst mode and other high-speed methods for accessing memory. The old systems sporting just an on-chip instruction cache, a moderate amount of DRAM and a hard drive have given way to sophisticated designs using multilevel memory architectures[3]. One of the primary building blocks of the multi-level memory architecture is the data cache.

There are many reasons to use an SRAM or a DRAM in a system design. Design tradeoffs include density, speed, volatility, cost, and features. All of these factors should be considered before you select a RAM for your system design.

### 1.1. Speed

The primary advantage of an SRAM over a DRAM is its speed. The fastest DRAMs on the market still require five to ten processor clock cycles to access the first bit of data. Although features such as EDO and Fast Page Mode have improved the speed with which subsequent bits of data can be accessed, bus performance and other limitations mean the processor must wait for data coming from DRAM[6]. Fast, synchronous SRAMs can operate at processor speeds of 250 MHz and beyond, with access and cycle times equal to the clock cycle used by the microprocessor. With a well-designed cache using ultra-fast SRAMs, conditions in which the processor has to wait for a DRAM access become rare.

### 1.2. Density

Because of the way DRAM and SRAM memory cells are designed, readily available DRAMs have significantly higher densities than the largest SRAMs[9]. Thus, when 64 Mb DRAMs are rolling off the production lines, the largest SRAMs are expected to be only 16 Mb.

### 1.3. Volatility

While SRAM memory cells require more space on the silicon chip, they have other advantages that translate directly into improved performance. Unlike DRAMs, SRAM cells do not need to be refreshed. This means they are available for reading and writing data 100% of the time.

#### 1.4. Cost

If cost is the primary factor in a memory design, then DRAMs win hands down. If, on the other hand, performance is a critical factor, then a well-designed SRAM is an effective cost performance solution.

### 1.5 Custom features

Most DRAMs come in only one or two flavors. This keeps the cost down, but doesn't help when you need a particular kind of addressing sequence, or some other custom feature. IBM's SRAMs are tailored, via metal and substrate, for the processor or application that will be using them. Features are connected or

disconnected according to the requirements of the user. Likewise, interface levels are selected to match the processor levels. IBM provides processor specific solutions by producing a chip with a standard core design, plus metal mask options to define feature sets.

Even though the SRAM is high Power Consuming Element to remove this unwanted power consumption a new Schmitt trigger based SRAM memory is proposed in our reference Paper. The proposed design is built after analyzing the different types of SRAM using low power design techniques the simulations were done under DSCH & Microwind Software.

- The Problem Found in the existing SRAM Designs are listed below:

- SRAMs are consuming most of the power of the core Processor Element.

- The leakage in the SRAM circuit is high when compared to the all other processor components.

- As its consuming much power heat dissipation also occurs

- So less efficient than all other elements.

#### II. Need of Schmitt Trigger Based SRAM Designs

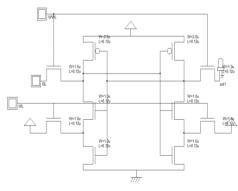

In order to resolve the conflicting read versus write design requirements in the conventional 6T bitcell, we apply the Schmitt Trigger (ST) principle for the cross-coupled inverter pair. A Schmitt trigger is used to modulate the switching threshold of an inverter depending on the direction of the input transition[10]. In the proposed ST SRAM bitcells, the feedback mechanism is used only in the pull-down path. During input transition, the feedback transistor (NF) tries to preserve the logic "1" at output (Vout ) node by raising the source voltage of pull-down nMOS (N1). This results in higher switching threshold of the inverter with very sharp transfer characteristics. Since a read-failure is initiated by a input transition for the inverter storing logic "1," higher switching threshold with sharp transfer characteristics of the Schmitt trigger gives robust read operation.

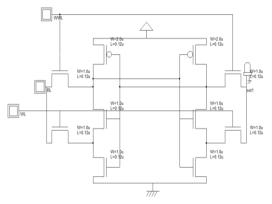

For the input transition, the feedback mechanism is not present. This results in smooth transfer characteristics that are essential for easy write operation. Thus, input-dependent transfer characteristics of the Schmitt trigger improves both read-stability as well as write-ability of the SRAM bitcell. Two novel bitcell designs are proposed. The first ST-based SRAM bitcell has been presented in our earlier work[5]. Another ST-based SRAM bitcell which further improves the bitcell stability has been reported in existing works. To maintain the clarity of the discussion, the ST bitcell in [5] is termed the "ST-1" bitcell while the other ST bitcell[10] is termed the "ST-2" bitcell shown in the Figures below.

Figure 1: ST2 Bit Cell

Figure 2: ST1 Bit Cell

### III. Need of 7T-SRAM for enhanced read stability

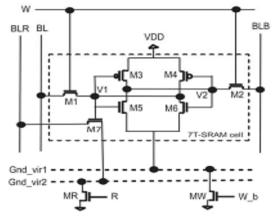

A conventional 6TSRAM cell design consists of a cross-coupled inverter pair (M3-M6) that does data storage and two access transistors (M1-M2) to load/retrieve data on bit lines, BL and BLB. During a write operation, the data is loaded on the bit lines and the word select signal WS is turned high. A successful write operation occurs if the data is correctly latched in the cell. The bit lines are pre-charged to the supply voltage and the word select line is turned high to retrieve data during a read operation. The bit line (BL) connected to the storage node (V1) storing a '0' gets discharged. The storage node (V1) rises above '0' during a read operation due to voltage division between the access transistor (M1) and the driver transistor (M6). A read failure can occur if the voltage drop rises higher than the threshold voltage of the inverter (M3, M5).

Figure 3: Virtual Grounding Based Read Error Reduced SRAM Cell

A conventional 6T-SRAM cell provides poor read stability since the access transistors provide direct access to the cell storage during a read operation. The proposed design (see Fig. 4) removes the access hazard during a read operation and therefore eliminates the chances of cell content being inadvertently flipped. It consists of a cross-coupled pair (M3-M6) for data storage as in case of a conventional 6T-SRAM cell. However the ground terminal of the inverter pair is connected to a virtual ground[2] (Gnd\_vir1) in the proposed design to provide high speed low-power write operation[7][8]. The word select line 'WS' is held high only during a write operation to load new data in the cell by turning on the write access transistors (M1-M2). A read access transistor (M7) connected to a virtual ground[9] (Gnd\_vir2) is used to retrieve data on read bit line (BLR) during a read operation. Our design decouples read/write operation using separate read/write access transistors. Therefore it doesn't suffer from constrained read/write requirements as in 6T-SRAM design.

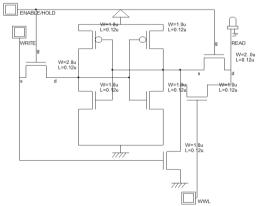

### IV. Results of Low Power 8T-SRAM

As the Schmitt trigger based designs are having high number of transistor to make the read stability that is 10 Transistor which very high when compared to the existing 6T SRAM Design we are going to combine the mentioned read stability at the above part to our proposed work to reduce the count than the Schmitt trigger based designs at the same time we are going to achieve reduced power consumption with reduced transistor count without affecting the read stability. At the same time the 8T-SRAM design supports separate read and write operations as in the Schmitt Trigger based designs. Our idea is to combine these to different technologies & to design a new circuit with much efficiency than the existing two designs.

Figure 4: Read Error Reduced 8T-SRAM Cell with Reduced Transistor Count

Figure 5: Layout Design of 8T-SRAM

Figure 6: Power Analysis of 8T-SRAM Design

Table1. Power/voltage consumption comparison

| 140101 | enter verwage comba | mption eo | iption companioon |  |

|--------|---------------------|-----------|-------------------|--|

| Sl. No | Bitcell Topologies  | Area      | Power             |  |

| 1      | ST-1 Bit cell       | 19X13     | 0.226mw           |  |

| 2      | ST-2 Bit cell       | 19X13     | 1.025µw           |  |

| 3      | 8T-ST SRAM          | 13X12     | 5.699µw           |  |

# V. Conclusion

Our design shows that much less power than the existing ones is  $5.699\mu$ w at the standard Our design layout combined with 6T & Virtual grounding with read error reduction Circuit concept 120nm technology. And it is having much reduced area than the conventional SRAM designs. Thus this design can be used for future SRAM core memories and Future Integrated circuits for low power and high speed applications using power gated circuits.

#### Reference

- [1] Mizuno, H. and T. Nagano, Driving source-line cell architecture for sub-1-V high-speed low-power applications. Solid-State Circuits, IEEE Journal of, 1996.31(4): p. 552-557.

- [2] Takeda, K., et al., A read-static-noise-margin-free SRAM cell for low-VDD and high-speed applications. Solid-State Circuits, IEEE Journal of, 2006.41(1): p. 113-121.

- [3] Chang, L., et al., An 8T-SRAM for Variability Tolerance and Low-Voltage Operation in High-Performance Caches. Solid-State circuits, IEEE Journal of, 2008.43(4): p. 956-963.

- [4] Tae-Hyoung, K., et al. A High-Density Subthreshold SRAM with Data-Independent Bitline Leakage and Virtual Ground Replica Scheme.inSolid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International. 2007.

- [5] J. P. Kulkarni, K. Kim and K. Roy "A 160mV robust Schmitt trigger based sub threshold SRAM," IEEE J. Solid-State Circuits, vol.42,no.10, pp.2303-2313, Oct.2007.

- [6] Bo, Z., et al. A Sub-200mV 6T SRAM in 0.13um CMOS.inSolid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International. 2007.

- [7] Wang, X., Roy, S., and Asenov, A., Impact of Strain on the Performance of high-k/metal replacement gate MOSFETs, in Proc. 10th Ultimate Integration on Silicon (ULIS 2009). 2009.

- [8] Kevin, Z., Embedded Memories for Nano-Scale VLSIs. 2009: Springer Publishing Company, Incorporated. 400.

- [9] Cheng, B., Roy, S., Roy, G., Brown, A., and Asenov, A. Impact of Random Dopant Fluctuation on Bulk CMOS 6-T SRAM Scaling. inSolid-State Device Research Conference, 2006. ESSDERC 2006.Proceeding of the 36th European. 2006.

- [10] Jawar Singh, D.K.P., Simon Hollis, and Saraju P. Mohanty, A single ended 6T SRAM cell design for ultra-low-voltage applications. IEICE Electronics Express, 2008.5(18): p. 750-755.

Lalitha Sowmya. M<sup>1</sup>, Asst. Prof in SSJ Engineering college, Hyderabad. She received her B. Tech degree in Electronics and Computer Management from JNTUH and M. Tech Degree in Electronics and Communication Engineering from JNTUH. She has 6 yrs of teaching experience. Her current interest includes VLSI & Embedded systems.

S. Jagadeesh<sup>2</sup>, Associate Professor and HOD in SSJ Engineering College, Hyderabad. He received his B. Tech Degree in Electronics & Communication Engineering from SKDU, Ananthapur and M. Tech Degree in Electronics and Communication Engineering from JNTUH, Hyderabad. He was a Research scholar in Electronics & communication Engineering Department, JNTUH. He has more than 15 years of experience in teaching and research. His current interest includes Digital image processing and electronics.

Lakavath. Mohan<sup>3</sup>, M. Tech-VLSI Student of SSJ Engineering College, JNTUH, Hyderabad. He is completed his B. Tech in Electronics and Communication Engineering from Vaagdevi Engineering College, JNTUH, Warangal. His current interest includes VLSI.