# **Random Test Program Generator for SPARC T1 Processor**

Nutan Hegde<sup>1</sup>, Lekha Pankaj<sup>2</sup>, Lyla B Das<sup>3</sup> <sup>1</sup>(ECE, KMCTCEW,Calicut, Kerala,India) <sup>2</sup>(ECE, AWH,Calicut,Kerala,India) <sup>3</sup>(ECE,NIT-C,Kerala,India)

**Abstract:** As the complexity of the microprocessor design is increasing the verification method is also becoming more and more complex. Unfortunately, it requires a long time to generate and run test sequences. Under the time to market pressure, it is very time consuming to write all test programs manually. This brings about the necessity of developing a random test program generator. The proposed method is for verifying the pre silicon model of the multithreaded multi cored processor (SPARC T1). The work takes the input from the user and generates a sequence of assembly language instructions (SPARC V9) randomly, initializes all the register values with random numbers to verify the corner cases. The test cases are seed based and run through the RTL model to check the correctness of the design. The test cases generated are also run on the defective model.

Keywords: SPARC, SPARC V9, RTPG, Defective model.

# I. Introduction

Open sourcing the hardware design of SPARC T1 processor by Sun Microsystem Inc. Inspired to study and analyze a 64 bit, 32 threads and 8 core processor. The insight of the design aspects, verification of the hardware design is achieved. Verification is a process to demonstrate that intent of a design is preserved in its implementation. Silicon capacity continues to increase enabling us to create and accommodate complex system within the same die. But the ability to verify larger and complex systems unfortunately has not kept in pace. Computer designs are so complicated these days that it can be impossible for humans to think through the entire testing space. At some point the people who write directed tests run out of testing concepts to implement. This rarely means that all the design problems have been found and fixed. Pseudo random test generators can often push the hardware designs harder by stimulating the logic under test in scenarios beyond the test developer's imagination. Automatic generation of test programs plays a major role in the verification of modern processors and hardware systems.

## II. Previous Work

Different algorithms are used to write the random test program generator depending on the complexity and problem faced in verification. The Model Based Test Generator comprises of an architectural model, a testing knowledge data-base, a behavioral simulator, architecture independent generator and a Graphical User Interface [1]. A pseudo random test system generates a processor instruction text file, containing a sequence of instructions in a target processor's assembly language [2]. Random test program generators for functional verification of processors were previously reported [3]. A random approach to automatic test generation for software and hardware verification has proved to be successful. It was applied to the verification of selected design units such as floating-point unit and even a complete processor, but very strong restrictions were imposed on the generated test programs [4]. The assumption behind these tools is that only a small subset of possible tests is simulated during functional verification. These tests are run through the design simulation model (the HDL model), and the results are compared with those predicted by the architecture specification represented by a behavioral simulator. Processor functional verification consists of two steps: 1) Generation of tests - for complex processors, this is done by automatic test generators which supply better productivity than manual tests. 2) Comparison between results computed by the two levels of simulation – both simulators are provided with the generated tests as stimuli, and the simulators final states are compared [1]. The test space of SPARC T1 processor design is so huge that it is very difficult to completely specify it.As a result, directed testing (special hand-coded test cases) alone would not be sufficient to find all the design defects. Hence a mechanism to derive assembly language test cases from higher level programs, such as C was developed to ease the test case development effort [3].Different algorithms are used to write the random test program generator depending on the complexity and problem faced in verification. A random approach to automatic test generation for software and hardware verification has proved to be successful. It was applied to the verification of selected design units such as floating-point unit and even a complete processor, but very strong restrictions were imposed on the generated test programs [4].

The test space of SPARC T1 processor design is so huge that it is very difficult to completely specify it .As a result, directed testing (special hand-coded test cases) alone would not be sufficient to find all the design defects. Hence a mechanism to derive assembly language test cases from higher level programs, such as C was developed to ease the test case development effort [3].

#### III. Proposed Methodology

The proposed method focuses on the study of SPARC instruction sets, registers based on SPARC V9 architecture. The test cases generated in SPARC assembly language based on the SPARC V9 architecture. The simulations are run at RTL level without the reference model. The proposed work mainly targets the EXU and LSU of SPARC processor.

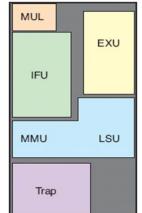

Fig1. Blocks of Sparc core.

Execution unit includes an arithmetic logic unit (ALU), shifter and the execute stage of the pipeline. It calculates memory and branch addresses. LSU includes memory and write back stages. Data cache maintains the order for cache updates, handles memory references between the SPARC core, the L1 data cache, and the L2 cache. All communication with the L2 cache is through the crossbar.

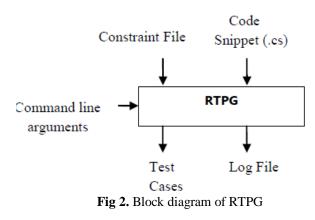

## IV. Implementation Of RTPG

The work creates a instruction set library. It initializes all the input registers using rand() function which returns a pseudo random number each time it is called. The RTPG randomly selects the instructions from the instruction library, checks the validity of the instruction, depending on the instruction the format of the instruction is done and writes it in the file. The file so formed is a test case. Each Test cases generated will have a seed number. Using this seed number the user can regenerate the test case. The user can get the seed value of any particular test case by using the log file which is an output file of RTPG. The log file contains the file names and its seed value generated by the generator. The generator developed can produce the test cases for specific constraints by specifying a user constraint file. The constraints file gives an opportunity to the user to put a restriction on the occurrence of any instruction. The RTPG has an additional option for the user, through which the user can introduce a code snippet which they want to test exclusively or any comments at the end of generated test cases. Fig 2. Shows the block diagram of the proposed work.

# 4.1 Interfaces To RTPG

The interfaces to the generator are command line, constraint file and the code snippet which the user wants to introduce exclusively to the test case.

#### 4.1.1 Command line arguments:

Executable file created is of the name RandGen.

Format of argument is RandGen -n <number of diags> -o <output filename> -cf<constraint file name.cf> -s < input seed value> -dir<output directory> -cs<code\_snippet.cs> -length <number of instructions>

## 4.1.2 Control/Constraint file:

After getting the command line arguments the particular control file is read for the additional information such as instruction weight, which specifies the weightage for individual instruction in the output from the RTPG i.e. the weight controls the frequency of the occurrence of the instructions in the test cases. Total weight will be sum of individual instructions.eg: add 10 (the weight for add instruction is 10/40 out of 40 instruction).

| Table 1: Options and f | functions of command | l line argument for RTPG |

|------------------------|----------------------|--------------------------|

| Tuble II options und I | .uncerons or commune | inne argument for rerr o |

| Option | Functions                                                                                                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -n     | Number of test cases. The user can specify the number of test cases to be generated. The Generator stops after that.                                                                                                                                   |

| -0     | Output filename. The user can give the test case name from this option. The generated testcases will have the name followed by the number from one upto the number of testcases mentioned by the user.                                                 |

| -cf    | Control/constraint file name. The user can mention the file name by which the generator has to take the input for the constraint.                                                                                                                      |

| -8     | Input seed value. It is an addition option if mentioned the generator will regenerate the test case with that particular seed value.                                                                                                                   |

| -cs    | Code snippet. This is also an additional option, if mentioned the file name specified in the option will be appended to<br>each of the testcases.<br>The user can use this option mainly to add some instructions exclusively or to add some comments. |

| -len   | Number of instructions. Each test case will have randomly generated instructions. It contains the number of instructions mentioned by this option.                                                                                                     |

## V. Result

The test cases were stored, and a diaglist was created to run all the test cases together hence came up with the regression suite. The test case snippet generated is in fig 3.

| setx 0x8110b28421afec29,%g1,%r11 |

|----------------------------------|

| setx 0xd8dc8e4c0356e8ea,%g1,%r12 |

| setx 0xeaf6bd3ee826095a,%g1,%r13 |

| setx 0x0cb84f93266af844,%g1,%r14 |

| xor %r2, 0x6f,%o0                |

| and %r1, %r4,%o6                 |

| sub %r3, %r1,%o4                 |

| addcc %r4, 0xef,%o6              |

| addcc %r3, 0xa9,%o1              |

| or %r4, %r2,%o0                  |

| sub %r3, 0xf6,%o1                |

| addcc %r1, 0xa5,%o6              |

| addcc %r0, %r5,%o0               |

|                                  |

Fig 3. Code snippet generated from RTPG.

#### 5.1 Simulation result

The generated test cases are run on the VCS (Verilog Compile and Simulator) from Synopsys. Under the name of each test case a directory will be created which holds the status and simulation files. Long simulations were conducted both on the defected and clean model. The results were monitored through log file. The status.log gives the information status of each testcase after running the regression. The log files shows exactly how the diag is formed including the reset, traps and main section of the program. The testcases which identifies the defect gives a bad trap. The status.log report gives the diag status. Fig 4 shows the Status.log of diags run in regression.

| Status:          | mytests | 1   | ALL | I |

|------------------|---------|-----|-----|---|

| PASS:            | 64      |     | 64  |   |

| FAIL:            | 0       | i - | 0   |   |

| Diag Problem:    | 1       | Í.  | 1   | 1 |

| License Problem: | 0       | 1   | 0   |   |

| MaxCycles Hit:   | 0       | 1   | 0   | 1 |

| Socket Problem:  | 0       | 1   | 0   |   |

| Timeout:         | 0       | 1   | 0   |   |

| LessThreads:     | 0       | 1   | 0   |   |

| Simics Problem:  | 0       | 1   | 0   |   |

| Performance:     | 0       | 1   | 0   |   |

| Killed By Job Q: | 0       | 1   | 0   |   |

| Unknown:         | 0       | 1   | 0   |   |

| UnFinished:      | 0       | 1   | 0   |   |

| flexlm error:    | 0       | L   | 0   | I |

| Diag Count:      | 65      |     | 65  |   |

Fig 4 Status.log run as regression suite

#### **5.1.1 Simulation timing:**

The simulation timing is analyzed, it is clear that the lesser the instruction lesser the simulation time. But different test cases take different time to identify a bug. Some test cases will go out of time.

| Instruction<br>Length | Simulation Time<br>(sec) | Cycles | Cycles/Sec |

|-----------------------|--------------------------|--------|------------|

| 20                    | 132.38                   | 14759  | 111.5      |

| 50                    | 133.67                   | 15089  | 112.9      |

| 1000                  | 167.27                   | 25495  | 152.4      |

Table 2: Simulation timing for different testcases

The testcases with and without div unit is also taken for the analysis. The testcases targeting the complex unit will take more time.

#### 5.1.2. Coverage Metrics

Coverage analysis was done using the CM View from the Synopsys which determines how well the test case is covering the design under test. The merged report gives the total coverage of all the test cases generated. It is also possible to test the coverage of individual test case. It is found that the testcases generated without the div instruction using the constraint file gives very less coverage of div module.

|   | Instance  | Medula         | Tytal C(%) | Logical C(%) | NonLogical C(%) | Event C(%) |

|---|-----------|----------------|------------|--------------|-----------------|------------|

| ¥ | 84        | spars_exu      |            |              |                 |            |

|   | alu       | IDAL DATE      | 110.00     |              | 101.00          |            |

|   | byylais . | spare_pau_bys  | 91.71      | •            | \$771           | -          |

|   | div       | sbitt_exiligiy | 16.09      |              | 10.01           |            |

|   | ec.c      | spurc_exu_ecc  | 51.47      | •            | \$5.47          | 2          |

|   | eci       | wirt_exu_ect   | 54.87      | 5427         | 6452            | -          |

| ø | đ         | bu_r_if        |            |              |                 |            |

|   | mi        | spure_exu_mi   | 44.35      | 4354         | (657            | -          |

|   | sht       | guire_exu_stat | 91.73      | 101.00       | \$1.15          |            |

Fig 5. Coverage report without div instruction

The result was compared with div instruction which gives max coverage to that module. The third row of div module with 10% increases to 100%.

| <u>A</u> dien Optimis                                   |             |               |           |              |                 |              |  |

|---------------------------------------------------------|-------------|---------------|-----------|--------------|-----------------|--------------|--|

|                                                         | Ector 4     |               |           |              |                 |              |  |

| Tobal Coverage 🖉 Contents of ectry, Jepting up an Users |             |               |           |              |                 |              |  |

| H <mark>ee</mark> stagi 🔒                               | heterox     | Modae         | Total CBJ | Logical C(%) | NonLegical (CS) | Events Citra |  |

| 😑 stag_qpjiptji                                         | <b>9</b> 64 | spart, esa    | 1         |              |                 |              |  |

| etag_qp_upt_1                                           | al.         | spart_exa_al. | 108.00    | -            | 100.300         | -            |  |

| S_top_patre                                             | bypess      | spart_ka_bys  | 10800     | -            | 100.000         | -            |  |

| S_dop_op_acts                                           | en.         | spare_exa_ds  | 1080.00   | -            | 100.300         | -            |  |

| 📒 stag_pcy_opt_0                                        | 800:        | spart_ska_ecc | 31.72     | -            | 61.72           | -            |  |

| 😑 stag_pci_ept_1                                        | ec          | spart_exa_ec  | 57.88     | 57.06        | ET 74           | F I          |  |

| 🗧 stag_pcy.jept;2                                       | 💋 🖬         | INCO1         |           |              |                 |              |  |

| - El stag_pcuipt_3                                      | and .       | spare_exa_mi  | 14. X     | 43.54        | 66.57           | -            |  |

| Merij Taelak (ja sta                                    | :10         | spact_ext_shi | 1080.00   | 10800        | 100.300         | -            |  |

| i férjjtekx_pata 📴                                      |             |               |           |              |                 |              |  |

| - · · · · · · · · · · · · · · · · · · ·                 |             |               |           |              |                 |              |  |

Fig 6. Coverage report with div instruction

#### VI. Conclusion And Future Scope

The ultimate goal of design verification is to ensure equivalence between a design and its functional specification. Processor/ASIC complexity, custom logic size and software contents are all increasing at such a pace that schedules are being squeezed and resources are being stretched. Presilicon verification today consumes about 70-80% of the design effort behind a processor/ASIC. Good presilicon verification methodology greatly minimizes the number of post silicon problems that can often be extremely difficult to debug. In time to market pressure it becomes necessary to go for automatic testcase generator.

Random test program generator targeting the arithmetic and logic, load and store unit can be extended to test all the other unit and core of the SPARC core to give deeper insight of the processor and troubleshooting mechanism.

#### References

- [1]. AharonAharon,Dave Goodman, Moshe Levinger, Yossi Lichtenstein,Yossi Malka, CharlotteMetzger, Moshe Molcho, Gil Shurek,Test Program Generation for Functional Verification of PowerPC Processors in IBM,

- Jeffery D. Whitman, System and method for generating pseudo random instruction for design verification USPatentdocuments, no 5, 572, 666, NOV 5, 1996.

- [3]. BabuTurumella, AimanKabakibo, ManjunathBogadi, Karunakara Menon et al, Design verification of a super-scalar RISC processor,Twenty-Fifth International Symposium on Fault –TolerantComputing, p.0472, IEEE, 1995

- [4]. A. Aharon, A.Bar David, B.Dorfman, E.Gofman, M.Leibowitz, V. Schwartzburd, Verification of the IBM RISC System / 6000 by a dynamic biased pseudo-random test program generator, IBM systems journal, Vol 30, no 4, 1991, pp 527-538

- [5] S. Mehta ,S. Ahmed, S. Al-Ashari, Dennis Chen, et al. Verification of the UltraSPARC<sup>™</sup>Microprocessor IEEE Computer Society Int'l conf., 1995, pp 452-461.

- [6]. IrithPomeranz, Nirmal R. Saxena, Richard Reeve, ParitoshKulkami, Generation of Test Cases for Hardware Design Verification of a Super-Scalar Fetch Processor, IEEE Int'l Test Conf., 1996, pp 904-913

- [7]. Samir Palnitkar, Verilog HDL-A guide to Digital Design and Synthesis ,First Edition, Pearson Education Asia, 2001.

- [8]. David L. Weaver, OpenSPARC<sup>™</sup> Internals, First Edition, Berkeley BSD systems, 2008, ISBN 978-0-557-01974-8, 2008.

- [9] David L. Weaver and Tom Germond The SPARC ArchitectureManual, Version 9, PTR Prentice Hall, ISBN 0-13-825001-4

- [10]. OpenSPARC<sup>™</sup> T1 Microarchitecture Specification, Copyright © 2006 Sun Microsystems, Inc.

- [11]. OpenSPARC™ T1 Processor Design and Verification User's Guide" Copyright 2008, Sun Microsystems, Inc.

- [12]. www.opensparc.net