# **SOC for detecting landmines**

# Krutika Keche, Prof.Mamta.M. Mahajan

(Electronics & telecommunication, G.H.Raisoni institute of engineering and technology for women/RTMNU,

India)

(Electronics & telecommunication, G.H.Raisoni institute of engineering and technology for women/RTMNU, India)

**Abstract :** The main objective of paper is to design and implement a high speed processing system with high throughput and low complexity. We are using system on chip using AMBA bus. This high speed processing system is application specific. This system will be used for landmine detection during wars as high speed processing is need of application. Firstly input processor will be designed as per the application. Then the concurrent processor will be designed. VHDL coding of the entire system on chip will be done. The simulation will be performed using Xilinx and FPGA. After the processing system is designed it will be compared to the conventional controller system. Thus proving that the system on chip is efficient and fast processing than the controller system.

**Keywords:** Advanced microcontroller bus architecture(AMBA)high performance bus, field programmable gate array(FPGA),landmine detection techniques, system on chip(SoCs).

## I. Introduction

In the field of semiconductor industry, there is continuous and remarkable progress in large scale integrated circuits. As a result there is increase in the complexity of circuit. Hence the design engineers have developed techniques and methodologies to deal with the complexity. One such technology is system on chip (SoC). The system on chip technology provides new level of integration on a single integrated circuit. With the help of SoC, designers have been able to deal with hardware and software codesign system. SoCs have various shapes and components. The main components of SoC are processor, interconnection bus, peripheral bus and many others. AMBA was introduced in 1977 originating from ARM processor and it is the standard bus system used in the industry. It consists of two level of hierarchy. It consists of two buses advanced high performance bus (AHB) and advanced peripheral bus(APB).AHB is used for high clock frequency and high performance system.APB is used for low power consumption devices and can be used along with AHB as well. The benefits of AMBA are it facilitates right first time development, technology independent, and modular system design, minimize the silicon area for both on and off chip communication. AMBA based SoC can be used and designed for various applications. One such application is for landmine detection. Various landmine methods are metal detector, electromagnetic method, acoustic or seismic methods, IR method, biological method and unmanned robot.

## 1.1. Previous work

AMBA based SoC can be designed as per the need of application. In the paper by Guoliang Ma and Hu He[1] design and implementation of advanced DMA controller have been discussed. Here DMAC architecture is used between AHB and APB bus. The data, address and control signal are controlled by DMAC.As a result AHB and APB bus operation running in parallel have been achieved. Another application is the paper by ShashisekharRamagundam, Sunil Das,ScottMortan,Satyaendra Biswas[2] where AMBA based memory controller with the help of AHB compliant memory controller have been proposed. Another application have been proposed by Zhenni Li, Jingjiao Li, Yue Zhao,ChaoqunRong[3] where they have implemented SoC design of dynamic image edge detection based on LEON3 open source processor. As the system has to deal with huge amount of data in a high speed, AMBA AHB bus is used. The various landmine detection techniques are discussed in the paper by C.P.Gooneratne, S.C Mukhopahyay, Sen Gupta[4]. The advantages and disadvantages of all the methods are presented.

## II. Proposed Plan

There are various technologies that have been used for landmine detection. Most of the methods are costly to implement and requires huge processing systems which increases the complexity and becomes difficult to use on the war field. In the proposed diagram we have designed innovative detection system to reduce false alarm and which can prove less fatal.

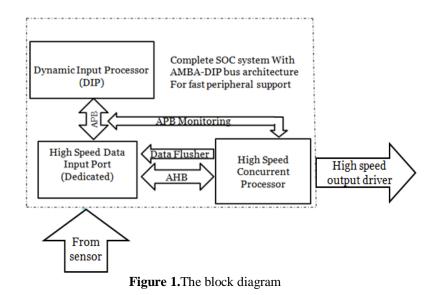

The block diagram consists of input port, input processor, concurrent processor and AMBA bus. All the blocks will be connected using AMBA AHB and APB bus. The data from the sensor will begiven to the input port where analog data will be converted to digital data and then to the input processor. Then it will be given to the concurrent processor where further processing will be done. After processing the explosive detection will be indicated on the output port. Then the data will be flushed out. Again APB bus will serially take the data to the input processor and again the process will repeated. Firstly input processor will be designed as per the application. Then the concurrent processor will be designed. VHDL coding of the entire system on chip will be done. After the processing system is designed it will be compared to the conventional controller system.

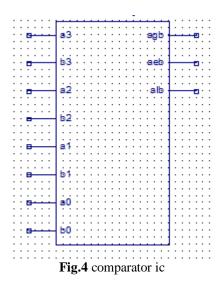

#### 3.1Comparator

## III. Components Designed

In the above block diagram given, for the input port we have designed comparator which will be used in the analog to digital converter. Analog to digital converter is required to convert the incoming analog signal to digital signal. Here the comparator will compare the incoming data from sensor and the data stored in the memory. We have designed 4-bit comparator IC.Using 4-bit comparator 8-bit comparator IC can be designed.

#### 3.2 Priority encoder

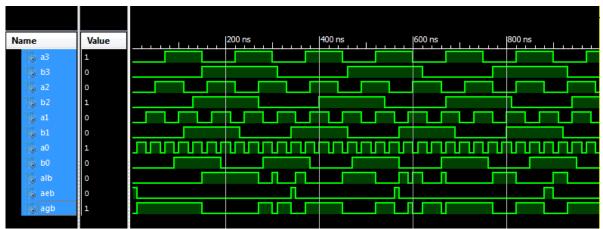

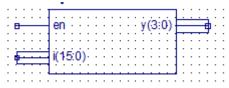

The analog to digital converter also consists of priority encoder to give the output in the digital form. After the comparator compares the incoming data with the data in the memory, it is given to the priority encoder to give the digital output. We have designed 16:4 priority encoder IC.

## 3.3 Memory

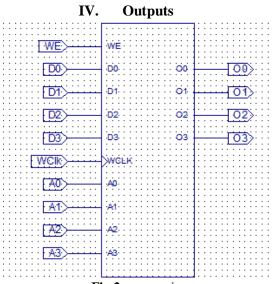

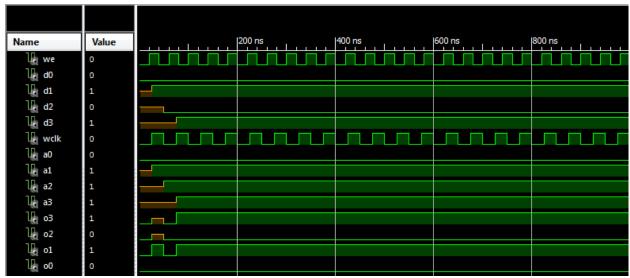

Random access memory is used in the dynamic input processor. RAM is used to store the data. Here in the proposed plan RAM is used to store the data permanently which will be compared to the incoming data from the sensor. We have designed 4-bit RAM IC.

Fig.3 memory output

Fig.5 comparator output

Fig.6 priority encoder ic

| Name        | Value    | <br>200 ns           | 400 ns                                      | 600 ns                | 800 ns |

|-------------|----------|----------------------|---------------------------------------------|-----------------------|--------|

| ▶ 🏹 i[15:0] | 00000000 | <u>00X00X000X000</u> |                                             | 0 10X 00 100X 0 10000 |        |

| 16 en       | 0        | mmm                  | hhhhhh                                      | Innnn                 |        |

| 🕨 📑 у[З:0]  | 2222     | <br>0 000000         | $\circ \circ \circ \circ \circ \circ \circ$ | 000000000             | 0000   |

|             |          |                      |                                             |                       |        |

|             |          |                      |                                             |                       |        |

Fig.7 priority encoder output

## V. Conclusion

The methods that are used for landmine detection can either prove to be fatal or destruction of expensive robot whose parts cannot be replaced or repaired. This processing system will result in high speed processing system with high throughput and low complexity. As a result it could be less fatal and cost effective.

#### References

- [1]. Guoliang Ma and Hu He, "Design and implementation of an advanced DMA controller on AMBA based SoC",2009 IEEE

- [2]. ShashisekharRamagundam, Sunil Das, Scott Morton, Satyendra Biswas," Design and implementation of high performance Master/Slave memory controller with microcontroller bus architecture",2014 IEEE.

- [3]. Zhenni Li, Jingjiao Li, Yue Zhao, ChaoqunRong," A SoC design and implementation of dynamic image detection based on the LEON3 open source processor",2013 IEEE.

- [4]. C. P. Gooneratne, S. C. Mukhopahyay and G. Sen Gupta," A Review of Sensing Technologies for Landmine Detection", 2nd International Conference on Autonomous Robots and Agents December 13-15, 2004 Palmerston North, New Zealand

- [5]. Ashutosh Singh, Anurag Shrivastava, G.S.Tomar," Design and implementation of high performance AHB reconfigurable arbiter for on chip bus architecture",2011 IEEE international conference on communication system and network technology

- [6]. Y. Hu and B. Yang, "Building an AMBA AHB compliant memory controller", Proceedings of the Third International Conference on Measuring Technology and Mechatronics Automation, 2011

- [7]. S. Rao and A. S. Phadke, "Implementation of AMBA compliant memory controller on a FPGA", International Journal of Emerging Trends in Electrical and Electronics, April 2013.

- [8]. FPGA PROTOTYPING BY VHDL EXAMPLES, Xilinx Spartan-3 Version, Pong P. Chu, Cleveland State University, A John Wiley & Sons, Inc., Publication 2008.

- [9]. VHDL Programming by Examples, Douglas L. Perry, Tata McGraw-Hill Publishing Company Limited.

- [10]. AHB Example AMBA System, Technical Reference Manual, ARM Inc., 1999.

- [11]. AMBA specification (rev 2.0), ARM Inc., 1999.