# Designing and Simulation of High- k , N-channel MOSFET devices using Tina Pro

Puja Acharya<sup>1</sup>, Shilpa Mehta<sup>2</sup>

<sup>1</sup>Assistant Professor, ECE Deptt K R Mangalam University Gurgaon, India <sup>2</sup>Assistant Professor, ECE Deptt K R Mangalam University Gurgaon, India

**Abstract**: This paper focuses on the development of 80nm channel length of high-k ( $TiO_2$ ) n-channel (NMOS) and p-channel (PMOS) enhancement mode MOSFETs which emerged due to replacement of SiO<sub>2</sub> by high-k ( $TiO_2$ ) MOSFETS, as there were many problems while using SiO<sub>2</sub> like high leakage current, short channel and electron tunneling effect.

**Keywords**: Simulation of the fabrication process was carried out by using Tina Pro Software to obtain more accurate process parameters & the results were then compared with NMOS using  $SiO_2$  as gate dielectric.

# I. INTRODUCTION

Here we will be discussing about the role of gate dielectric in (MOSFET) devices, and their criteria for the selection of high-k materials. Furthermore, materials preferred for gate dielectrics both high-k & low-k materials. So, to start with gate dielectrics which is the one used between its gate and substrate. When any metal and a semiconductor or any dielectrics form an interface, charge transfer takes place across the interface. In state-of-the-art processes, the gate dielectric is subjected to its important role, including [6]:

- a) Interface to the substrate is electrically cleaned.

- b) High capacitance is required to increase the trans- conductance of MOSFET device.

- c) To avoid dielectric breakdown and leakage due to quantum tunneling, high thickness of channel is required.

The capacitance and thickness constraints directly oppose each other. For silicon based substrate MOSFETs, the gate dielectric considered is  $SiO_2$  as it offers high impedance. As we know thermal oxide has a very clean interface [6].

MOSFETs are backbone of the integrated-circuit industry till date. The reason behind is the perfection of the SiO2/Si interface. As MOSFET dimensions have scaled, correspondingly larger values of the oxide capacitance (Cox) are required. The oxide capacitance is mandatory for inverting the surface to a sufficient sheet charge density in order get the desired current for the particular given supply voltage and for avoiding short channel behavior [6].

Here some of the defects are formed in the gate oxide at the SiO2/Si interface due to flow of charge carriers. The solution to this can be an insulator with higher dielectric constant whose properties can be dependent on the material as well as on the processing technology. Initial high-k dielectric was TiO<sub>2</sub> and later on other dielectrics were introduced by many researchers like Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, ZrSi<sub>x</sub>O<sub>y</sub>, Y<sub>2</sub>O<sub>3</sub>, Ya<sub>2</sub>O<sub>3</sub> for submicron MOSFET [5].

# II. CRITERIA FOR SELECTION OF GATE DIELECTRIC

As silicon dioxide  $(SiO_2)$  has excellent dielectric properties that lead to the evolution of microelectronics during the past decades.[5] Due to reduction in feature size integrated circuit performance has been improved, but there are some disadvantages due to scaling factor. So, there emerged a need for high dielectric constant rather than using SiO<sub>2</sub>.

# III. Materials Selected For Gate Dielectric

Based on strength of material dielectric is divided in two categories namely: Low-k and High-k.

## A. LOW-k

A low-k as the name specifies the one with small dielectric constant. Although there is availability of large number of materials with lower dielectric constants but in terms of integrity to a manufacturing process only some of them are suitable. So, efforts have been made in direction of these classes of materials [2]. Some of these materials are defined below:

a) Fluorine-doped Silicon Dioxide

Here,  $SiO_2$  doping is done with fluorine in order to generate fluorinated silica glass, dielectric constant range is from 3.9 to 3.5 [1].

b) Carbon-doped Silicon dioxide

Here, doping of  $SiO_2$  with carbon is done, dielectric constant is 3.0 [5].

c) Porous Silicon dioxide

Different methods are applied for creating larger voids or pores in  $SiO_2$  dielectric. Voids may have a dielectric constant of approximately 1, so the dielectric constant of the porous material can be reduced by raising the porosity of the film.

d) Porous Carbon-doped Silicon dioxide

By UV curing method, methyl groups in carbon doped silicon dioxide can be removed and pores can be defined to the carbon doped silicon dioxide low-k materials [4].

#### B. High-k

The term high-k dielectric defines a material with a high dielectric constant k that will allow increase in gate capacitance without the associated leakage effects. Such dielectric constants are defined below:

#### a) Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>)

This material has following characteristics like high permittivity, high band gap, high band discontinuities, and good break down voltage. But the main problem is that the high processing temperatures (1000°C) the mobility of electrons shows a flat band voltage shift in the positive direction.

#### b) Titanium dioxide (TiO<sub>2</sub>)

This is an alternative gate dielectric material suitable for deep submicron MOSFET applications. It is advantageous too as it has dielectric constant of 80, bandgap as 3.5eV for amorphous films and 3.2 eV for crystalline films which are good for acting as an insulator.

#### c) Zirconium oxide (ZrO<sub>2</sub>)

$ZrO_2$  is referred due to its dielectric constant (k~25) higher band gap (~5.8eV). It is thermodynamically stable with Si, but crystallization temperature is about 500°C, which is low for ULSI processing.

| Gate Dielectric                | Dielectric constant | Energy Band | Conduction Band Offset | Valence Band     |

|--------------------------------|---------------------|-------------|------------------------|------------------|

| Material                       | (k)                 | Gap         | $\Delta Ec (eV)$       | Offset           |

|                                |                     | Eg (eV)     |                        | $\Delta Ec (eV)$ |

| SiO <sub>2</sub>               | 3.9                 | 9           | 3.5                    | 4.4              |

| Al <sub>2</sub> O <sub>3</sub> | 8                   | 8.8         | 3                      | 4.7              |

| TiO <sub>2</sub>               | 80                  | 3.5         | 1.1                    | 1.3              |

| ZrO <sub>2</sub>               | 25                  | 5.8         | 1.4                    | 3.3              |

| HfO <sub>2</sub>               | 25                  | 5.8         | 1.4                    | 3.3              |

| Ta <sub>2</sub> O <sub>5</sub> | 25                  | 6           | 1.5                    | 3.4              |

| Y <sub>2</sub> O <sub>3</sub>  | 13                  | 6           | 2.3                    | 2.6              |

| Ya <sub>2</sub> O <sub>3</sub> | 27                  | 4.3         | 2.3                    | 0.9              |

Table 1: High-k dielectric materials and their properties

## IV. Role Of Simulation Software

TINA is an acronym of "Toolkit for Interactive Network Analysis". TINA Design Suite is a powerful and affordable circuit simulator and PCB design software package for analyzing, designing, and real time testing of analog, digital, HDL, MCU, and mixed electronic circuits and their PCB layouts. It also analyzes SMPS, RF, communication, and opto-electronic circuits which generate and debug MCU code using the integrated flowchart tool and also test microcontroller applications in a mixed circuit environment. A unique feature of TINA is that it can bring the circuit to run with the optional USB controlled TINA Lab II and Lab Xplorer hardware, which turns the computer into a powerful, multifunction T&M instrument.

# V. Simulation Results

Simulations of the both high-k devices (NMOS and PMOS) are done by using Tina Pro. Device simulation is done for calculating the electrical behavior of semiconductor devices. It also helps in calculating some of the design parameters such as sheet resistance, channel surface concentration, gate oxide thickness.

## a. Determination of Threshold voltage

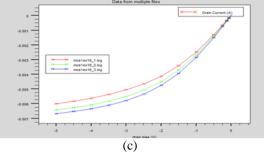

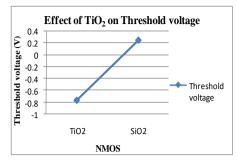

Threshold voltage is the one which determines the requirements for turning the transistor on or off. According to the simulation results, the threshold voltage for NMOS with TiO2 is around to -0.74V while for

NMOS with SiO2,  $V_t$  is equal to 0.23V and for PMOS with TiO2,  $V_t$  is equal to -0.24V. Figure shows the  $I_d$ - $V_g$  characteristics for the transistors with  $V_t$ .

Figure2: The I<sub>d</sub>-V<sub>g</sub> curve for (a) NMOS with SiO<sub>2</sub> as gate dielectric (b) NMOS with TiO<sub>2</sub> as gate dielectric and (c) PMOS with TiO<sub>2</sub> as gate dielectric; obtained from Tina Pro simulator.

b. MOSFET V-I Characteristics

Figure 3: Family of I<sub>d</sub> vs. V<sub>gs</sub> curve for (a) NMOS with SiO<sub>2</sub> as gate dielectric (b) NMOS with TiO<sub>2</sub> as gate dielectric; obtained from Tina Pro simulator.

c. Effect of Drain Voltage and Threshold Voltage

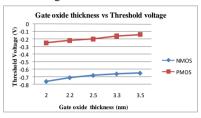

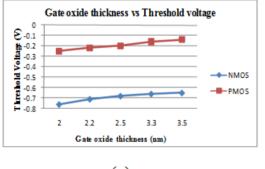

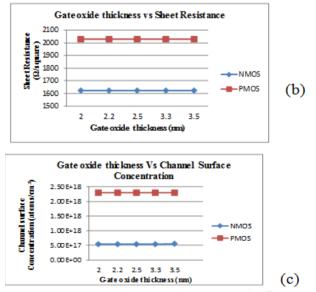

d. Effect of gate oxide thickness on device parameters like Threshold voltage, Sheet resistance and Channel Surface concentration.

FIG 4: EFFECT OF GATE OXIDE THICKNESS ON DEVICE PARAMETERS (A) THRESHOLD VOLTAGE (B) SHEET RESISTANCE (C) CHANNEL SURFACE CONCENTRATION

## E. EFFECT OF HIGH-K ON THRESHOLD VOLTAGE

Fig 5: Effect of High-k on Threshold voltage

#### References

- [1]. Chih Chin Yang, Lan Hui Huang, Bo Shum Chen, Jia Liang Ke, and Chung Lun Tsai National Kaohsiung Marine University, Department of Microelectronics Engineering, Kaohsiung, Taiwan, World Academy of Science, Engineering and Technology, "Inductance Characteristic of Annealed Titanium Dioxide on Silicon Substrate", World Academy of Science, Engineering and Technology, vol. 56, pp. 1-2, 2009.

- [2]. Davinder Rathee, Sandeep K Arya, Department of Electronics and Communication Engineering, Guru Jambheshwar University of Science & Technology, Hisar, India, Mukesh Kumar, Department of Electronics Science, Kurukshetra University, Kurukshetra, India, "CMOS Development and Optimization, Scaling Issue and Replacement with High-k Material for Future Microelectronics", International Journal of Computer Applications, vol. 8, no. 5, pp. 10-11, October 2011.

- [3]. Davinder Rathee, Sandeep K Arya, Department of Electronics and Communication Engineering, Guru Jambheshwar University of Science & Technology, Hisar, India, Mukesh Kumar, Department of Electronics Science, Kurukshetra University, Kurukshetra, India, Higher Education Press and Springer-Verlag Berlin Heidelberg, "Analysis of TiO<sub>2</sub> for microelectronic applications: effect of deposition methods on their electrical properties", Front. Optoelectronics, China, vol. 4, no. 349–358, pp. 1, 2011.

- [4]. Davinder Rathee, Sandeep K Arya, Department of Electronics and Communication Engineering, Guru Jambheshwar University of Science & Technology, Hisar, India, Mukesh Kumar, Department of Electronics Science, Kurukshetra University, Kurukshetra, "Capacitance-voltage analysis of a high-k dielectric on silicon", Journal of Semiconductors, Chinese Institute of Electronics, vol. 33, no. 2, pp. 1-2, 2012.

- [5]. J. R. Hauser and K. Ahmed Department of Electrical and Computer Engineering, North Carolina State University, Raleigh, NC 27695 American Institute of Physics, "Characterization of ultra-thin oxides using electrical C-V and I-V measurements", International Conference for the American Institute of Physics, vol. 235, pp. 1-2, 5, 1998.

- [6]. Keithley Application Notes series, Keithley Instruments, Incorporation, "C-V Characterization of MOS Capacitors Using the Model 4200-SCS Semiconductor Characterization System", no. 2896, pp. 1, 6-10, Dec 2007.